Motorola MPC8260 User Manual

Page 291

MOTOROLA

Chapter 10. Memory Controller

10-15

Part III. The Hardware Interface

23

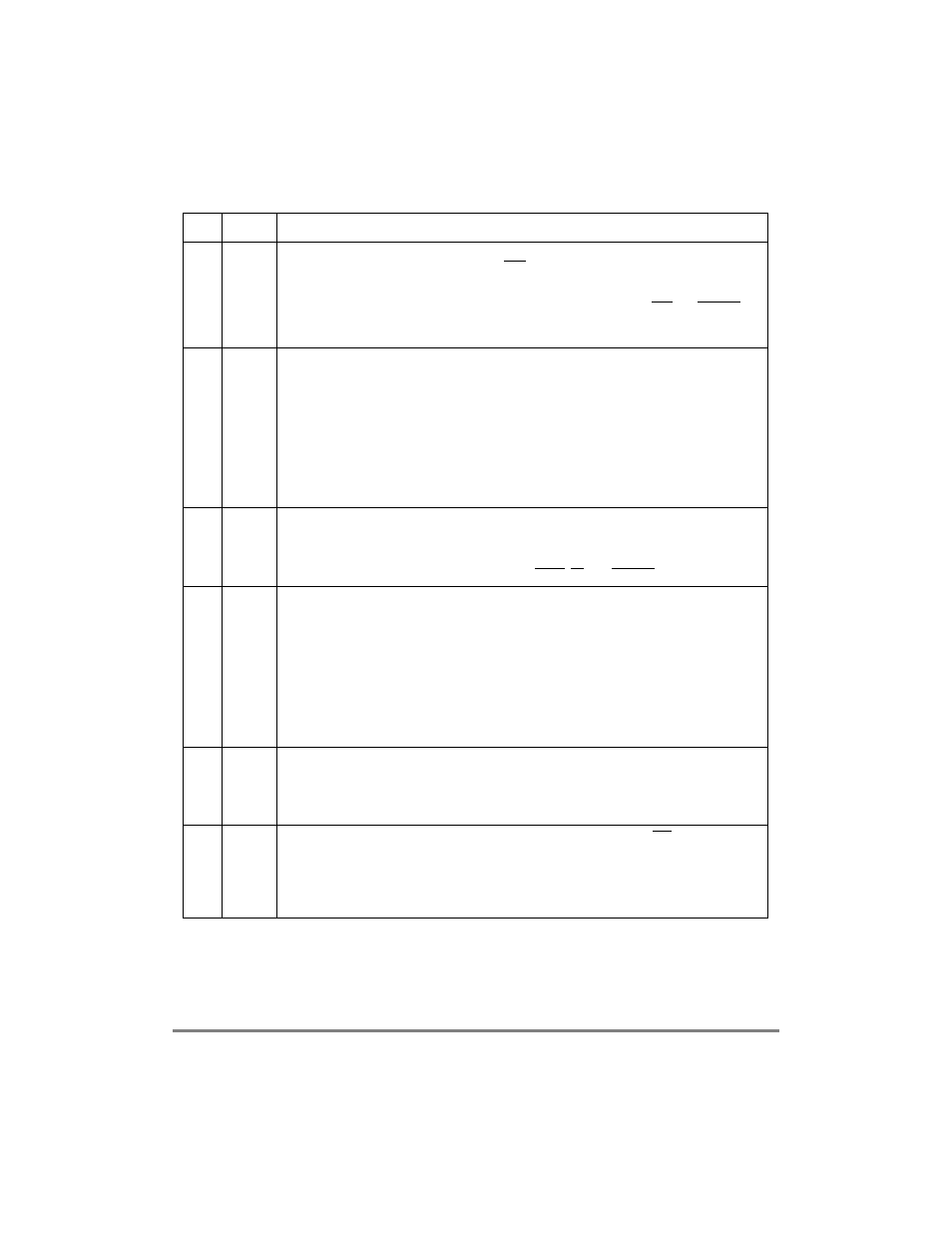

WP

Write protect. Can restrict write accesses within the address range of a BR. An attempt to write to

this address range while WP = 1 can cause TEA to be asserted by the bus monitor logic (if

enabled) which terminates the cycle.

0 Read and write accesses are allowed.

1 Only read accesses are allowed. The memory controller does not assert CSx and PSDVAL on

write cycles to this memory bank. MSTAT[WPER] is set if a write to this memory bank is

attempted.

24Ð26

MS

Machine select. speciÞes machine select for the memory operations handling and assigns the

bank to the 60x or local bus if GPCM or SDRAM are selected. If UPMx is selected, the bus

assignment is determined by MxMR[BSEL].

000 GPCMÑ60x bus (reset value)

001 GPCMÑlocal bus

010 SDRAMÑ60x Bus

011 SDRAMÑlocal bus

100 UPMA

101 UPMB

110 UPMC

111 Reserved

27

EMEMC External MEMC enable. Overrides MSEL and assigns the bank to the 60x bus. However, other

BRx Þelds remain in effect. See Section 10.2.10, ÒExternal Memory Controller Support.Ó

0 Access are handled by the memory controller according to MSEL.

1 Access are handled by an external memory controller (or other slave) on the 60x bus. The

external memory controller is expected to assert AACK, TA, and PSDVAL.

28Ð29

ATOM

Atomic operation. See Section 10.2.8, ÒAtomic Bus Operation.Ó

00 The address space controlled by the memory controller bank is not used for atomic operations.

01 Read-after-write-atomic (RAWA).Writes to the address space handled by the memory

controller bank cause the MPC8260 to lock the bus for the exclusive use of the master. The

lock is released when the master performs a read operation from this address space. This

feature is intended for CAM operations.

10 Write-after-read-atomic (WARA). Reads from the address space handled by the memory

controller bank cause the MPC8260 to lock the bus for the exclusive use of the accessing

device. The lock is released when the device performs a write operation to this address space.

11 Reserved

Note that If the device fails to release the bus, the lock is released after 256 clock cycles.

30

DR

Data pipelining. See Section 10.2.9, ÒData Pipelining.Ó

0 No data pipelining is done.

1 Data beats of accesses to the address space controlled by the memory controller bank are

delayed by one cycle. This feature is intended for memory regions that use ECC or parity checks

and need to improve data setup time.

31

V

Valid bit. Indicates that the contents of the BRx and ORx pair are valid. The CS signal does not

assert until V is set.

0 This bank is invalid.

1 This bank is valid

Notes: An access to a region that has no V bit set may cause a bus monitor time-out. After a

system reset, BR0[V] is set.

Table 10-3. BRx Field Descriptions (Continued)

Bits

Name

Description