Motorola MPC8260 User Manual

Page 124

3-4

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part I. Overview

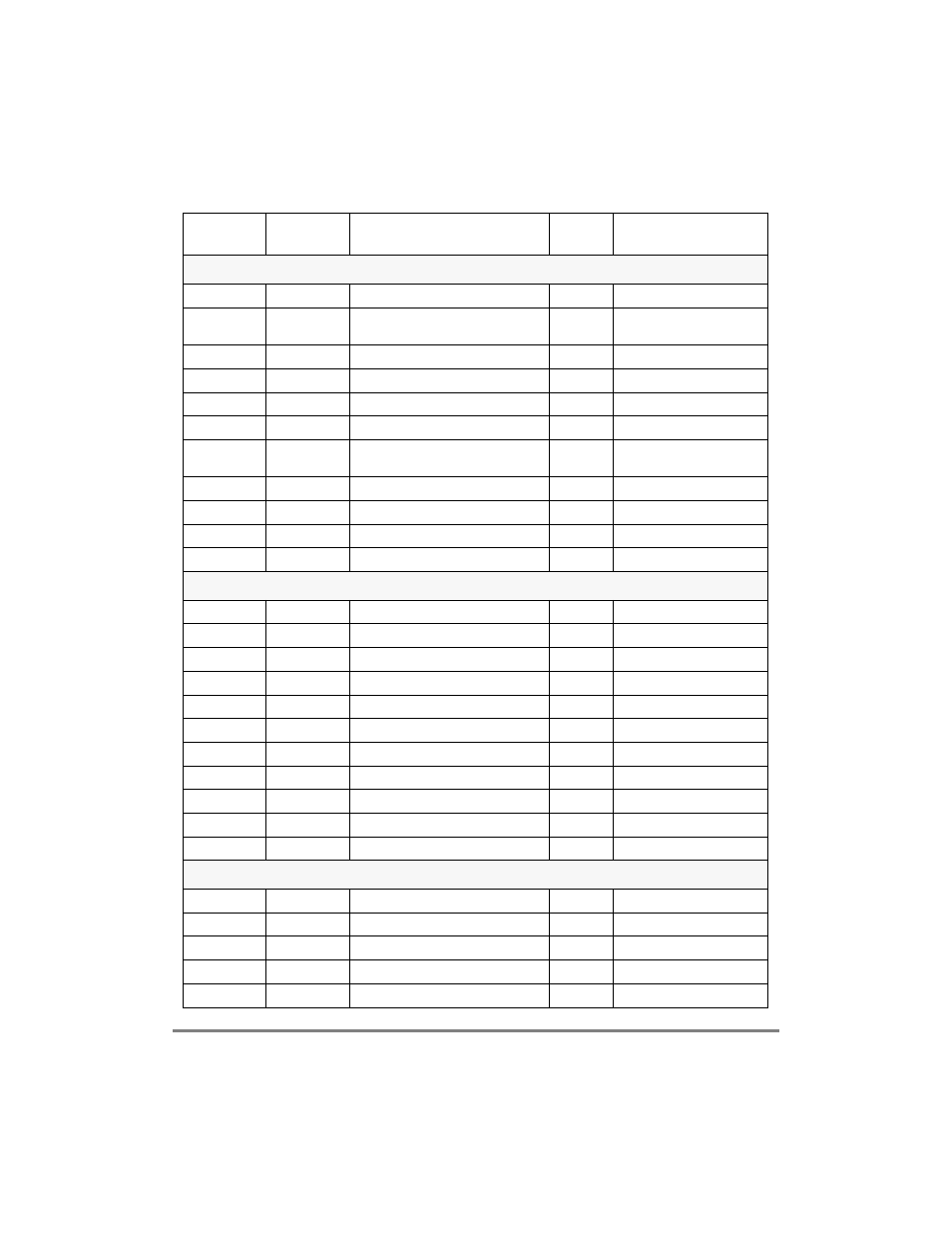

System Integration Timers

10200Ð10 21F

Reserved

Ñ

32 bytes

10220

TMCNTSC

Time counter status and control

register

16 bits

10224

TMCNT

Time counter register

32 bits

10228

Reserved

Ñ

32 bits

Ñ

1022C

TMCNTAL

Time counter alarm register

32 bits

10230Ð1023F

Reserved

Ñ

16 bytes

Ñ

10240

PISCR

Periodic interrupt status and control

register

16 bits

10244

PITC

Periodic interrupt count register

32 bits

10248

PITR

Periodic interrupt timer register

32 bits

1024CÐ102A8

Reserved

Ñ

94 bytes

Ñ

102AAÐ10BFF Reserved

Ñ

2,390bytes Ñ

Interrupt Controller

10C00

SICR

SIU interrupt conÞguration register

16 bits

10C04

SIVEC

SIU interrupt vector register

32 bits

10C08

SIPNR_H

SIU interrupt pending register (high)

32 bits

10C0C

SIPNR_L

SIU interrupt pending register (low)

32 bits

10C10

SIPRR

SIU interrupt priority register

32 bits

10C14

SCPRR_H

CPM interrupt priority register (high)

32 bits

10C18

SCPRR_L

CPM interrupt priority register (low)

32 bits

10C1C

SIMR_H

SIU interrupt mask register (high)

32 bits

10C20

SIMR_L

SIU interrupt mask register (low)

32 bits

10C24

SIEXR

SIU external interrupt control register

32 bits

10C28Ð10C7F Reserved

Clocks and Reset

10C80

SCCR

System clock control register

32 bits

10C88

SCMR

System clock mode register

32 bits

10C90

RSR

Reset status register

32 bits

10C94

RMR

Reset mode register

32 bits

10C98Ð10CFF Reserved

Ñ

104 bytes

Ñ

Table 3-1. Internal Memory Map (Continued)

Internal

Address

Abbreviation

Name

Size

Section/Page Number