Motorola MPC8260 User Manual

Page 123

MOTOROLA

Chapter 3. Memory Map

3-3

Part I. Overview

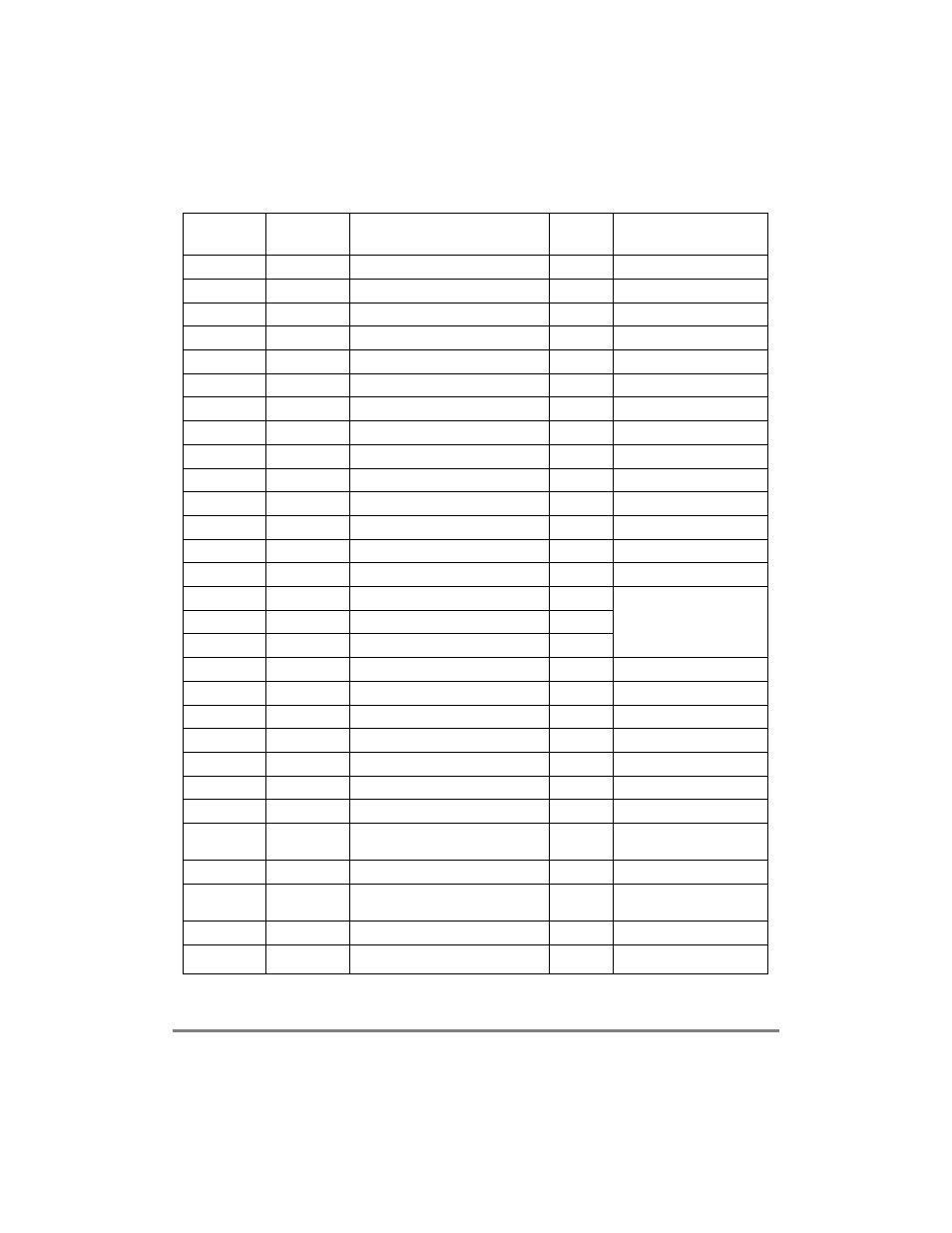

10134

OR6

Option register bank 6

32 bits

10138

BR7

Base register bank 7

32 bits

1013C

OR7

Option register bank 7

32 bits

10140

BR8

Base register bank 8

32 bits

10144

OR8

Option register bank 8

32 bits

10148

BR9

Base register bank 9

32 bits

1014C

OR9

Option register bank 9

32 bits

10150

BR10

Base register bank 10

32 bits

10154

OR10

Option register bank 10

32 bits

10158

BR11

Base register bank 11

32 bits

1015C

OR11

Option register bank 11

32 bits

10160 Reserved

Ñ

8

bytes

Ñ

10168

MAR

Memory address register

32 bits

1016C

Reserved

Ñ

32 bits

Ñ

10170

MAMR

Machine A mode register

32 bits

10174

MBMR

Machine B mode register

32 bits

10178

MCMR

Machine C mode register

32 bits

1017C

Reserved

Ñ

48 bits

Ñ

10184

MPTPR

Memory periodic timer prescaler

16 bits

10188

MDR

Memory data register

32 bits

1018C

Reserved

Ñ

32 bits

Ñ

10190

PSDMR

60x bus SDRAM mode register

32 bits

10194

LSDMR

Local bus SDRAM mode register

32 bits

10198

PURT

60x bus-assigned UPM refresh timer

8 bits

1019C

PSRT

60x bus-assigned SDRAM refresh

timer

8 bits

101A0

LURT

Local bus-assigned UPM refresh timer 8 bits

101A4

LSRT

Local bus-assigned SDRAM refresh

timer

8 bits

101A8

IMMR

Internal memory map register

32 bits

101ACÐ101FF

Reserved

Ñ

84 bytes

Ñ

Table 3-1. Internal Memory Map (Continued)

Internal

Address

Abbreviation

Name

Size

Section/Page Number