Risc controller configuration register (rccr) -8, Rccr bit þelds are described in table 13-3 – Motorola MPC8260 User Manual

Page 438

13-8

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part IV. Communications Processor Module

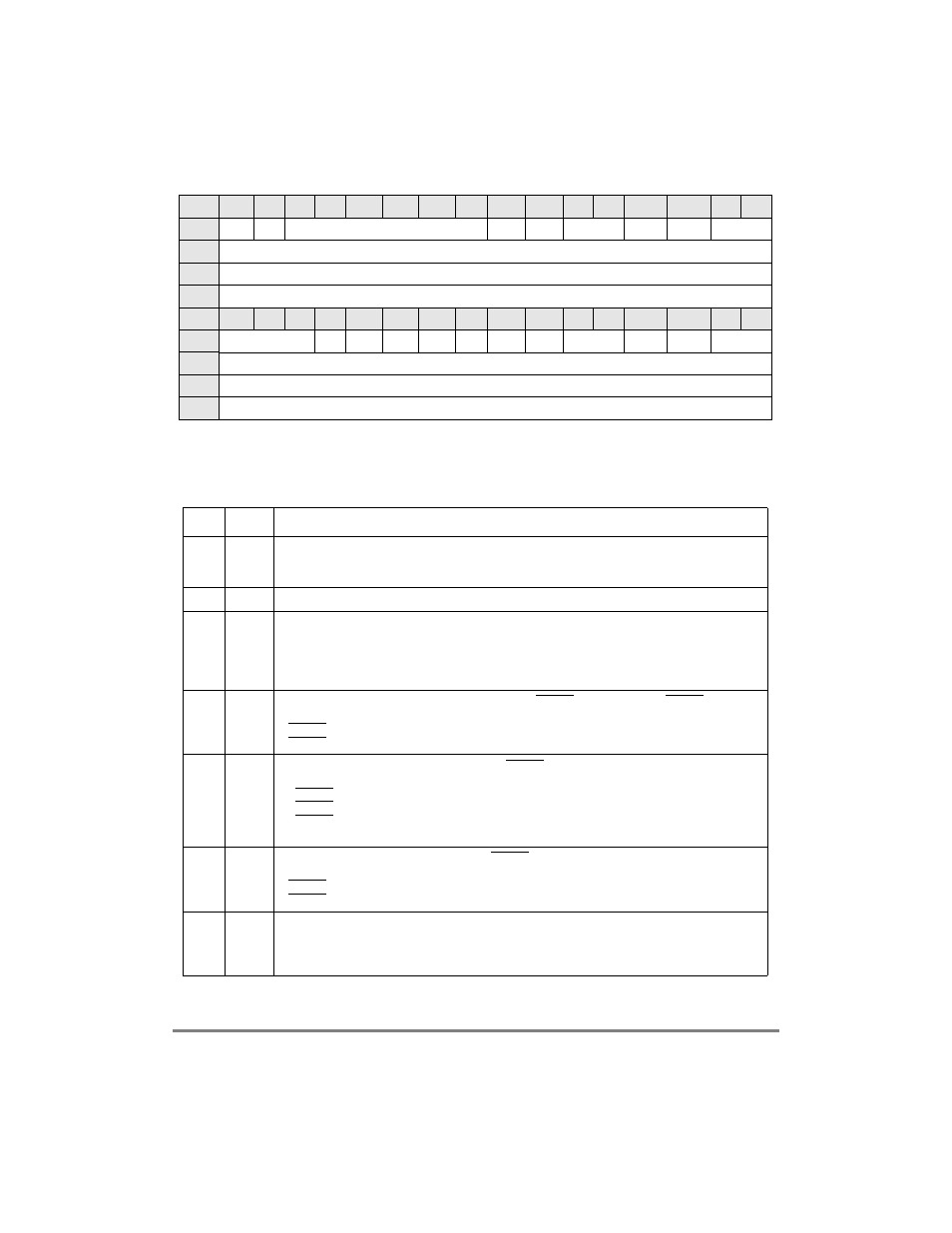

RCCR bit Þelds are described in Table 13-3.

Bits

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Field

TIME

Ñ

TIMEP

DR1M DR2M

DR1QP

EIE

SCD

DR2QP

Reset

0000_0000_0000_0000

R/W

R/W

Addr

Bits

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

Field

ERAM

Ñ

EDM1 EDM2 EDM3

EDM

4 DR3M DR4M

DR3QP

DEM12 DEM34

DR4QP

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0X119C6

Figure 13-3. RISC Controller Configuration Register (RCCR)

Table 13-3. RISC Controller Configuration Register Field Descriptions

Bits

Name Description

0

TIME

Timer enable. Enables the CP internal timer that generates a tick to the CP based on the value

programmed into the TIMEP Þeld. TIME can be modiÞed at any time to start or stop the scanning of

the RISC timer tables.

1

Ñ

Reserved

2Ð7

TIMEP

Timer period controls the CP timer tick. The RISC timer tables are scanned on each timer tick and

the input to the timer tick generator is the general system clock (133/166MHZ) divided by 1,024.

The formula is (TIMEP + 1)

´ 1,024 = (general system clock period). Thus, a value of 0 stored in

these bits gives a timer tick of 1

´ (1,024) = 1,024 general system clocks and a value of 63

(decimal) gives a timer tick of 64

´ (1,024) = 65,536 general system clocks.

8, 9,

24, 25

DRxM

IDMAx request mode. Controls the IDMA request x (DREQx) sensitivity mode. DREQx is used to

activate IDMA channel x. See Section 18.7, ÒIDMA Interface Signals.Ó

0 DREQx is edge sensitive (according to EDMx).

1 DREQx is level sensitive.

10Р11,

14Р15,

26Р27,

30Р31

DRxQP

IDMAx request priority. Controls the priority of DREQx relative to the communications controllers.

See Section 18.7, ÒIDMA Interface Signals.Ó

00 DREQx has more priority than the communications controllers (default).

01 DREQx has less priority than the communications controllers (option 2).

10 DREQx has the lowest priority (option 3).

11 Reserved

12

EIE

External interrupt enable. When EIE is set, DREQ1 acts as an external interrupt to the CP.

ConÞgure as instructed in the download process of a Motorola-supplied RAM microcode package.

0 DREQ1 cannot interrupt the CP.

1 DREQ1 will interrupt the CP.

13

SCD

Scheduler conÞguration. ConÞgure as instructed in the download process of a Motorola-supplied

RAM microcode package.

0 Normal operation.

1 Alternate conÞguration of the scheduler.