Chapter33 serial peripheral interface (spi), Chapter 33, Serial peripheral interface (spi) – Motorola MPC8260 User Manual

Page 925: Spi block diagram -1, Chapter 33, òserial peripheral interface (spi), Chapter 33 serial peripheral interface (spi)

MOTOROLA

Chapter 33. Serial Peripheral Interface (SPI)

33-1

Chapter 33

Serial Peripheral Interface (SPI)

330

330

The serial peripheral interface (SPI) allows the MPC8260 to exchange data between other

MPC8260 chips, the MPC860, the MC68360, the MC68302, the M68HC11 and M68HC05

microcontroller families, and peripheral devices such as EEPROMs, real-time clocks, A/D

converters, and ISDN devices.

The SPI is a full-duplex, synchronous, character-oriented channel that supports a four-wire

interface (receive, transmit, clock and slave select). The SPI block consists of transmitter

and receiver sections, an independent baud-rate generator, and a control unit. The

transmitter and receiver sections use the same clock, which is derived from the SPI baud

rate generator in master mode and generated externally in slave mode. During an SPI

transfer, data is sent and received simultaneously.

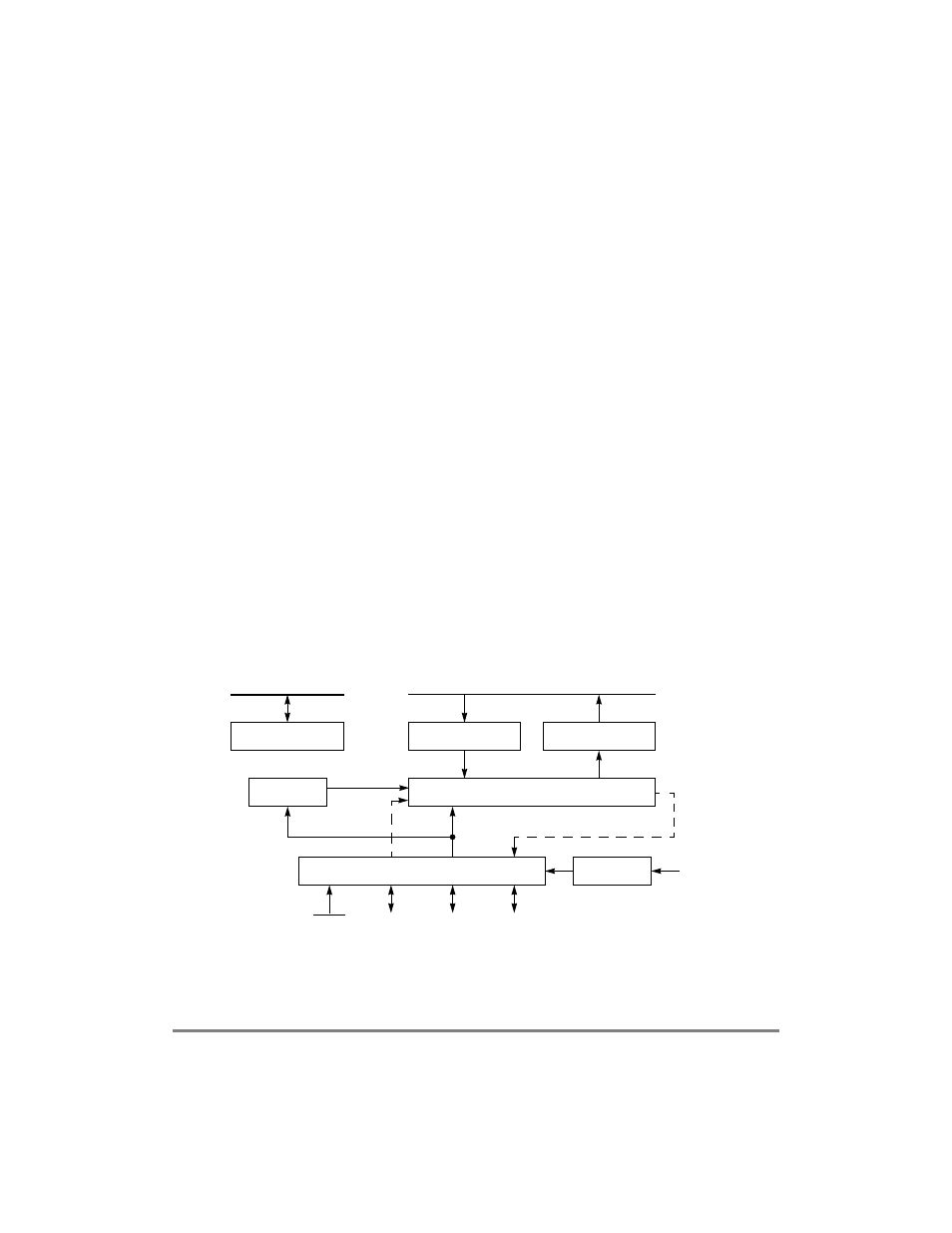

Because the SPI receiver and transmitter are double-buffered, as shown in Figure 33-1, the

effective FIFO size (latency) is 2 characters. The SPIÕs msb is shifted out Þrst. When the

SPI is disabled in the SPI mode register (SPMODE[EN] = 0), it consumes little power.

Figure 33-1. SPI Block Diagram

SPI Mode Register

Transmit_Register

Receive_Register

Counter

Shift_Register

SPIBRG

Pins Interface

BRGCLK

SPIMOSI

SPISEL

SPIMISO

SPICLK

TxD

RxD

IN_CLK

60x Bus

Peripheral Bus