9 software service register (swsr), Software service register (swsr) -36, Tescr1 field descriptions -36 – Motorola MPC8260 User Manual

Page 174

4-36

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part II. ConÞguration and Reset

4.3.2.9 Software Service Register (SWSR)

The software service register (SWSR) is the location to which the software watchdog timer

servicing sequence is written. To prevent software watchdog timer time-out, the user should

write 0x556C followed by 0xAA39 to this register, which resides at 0x1000E. SWSR can

be written at any time, but returns all zeros when read.

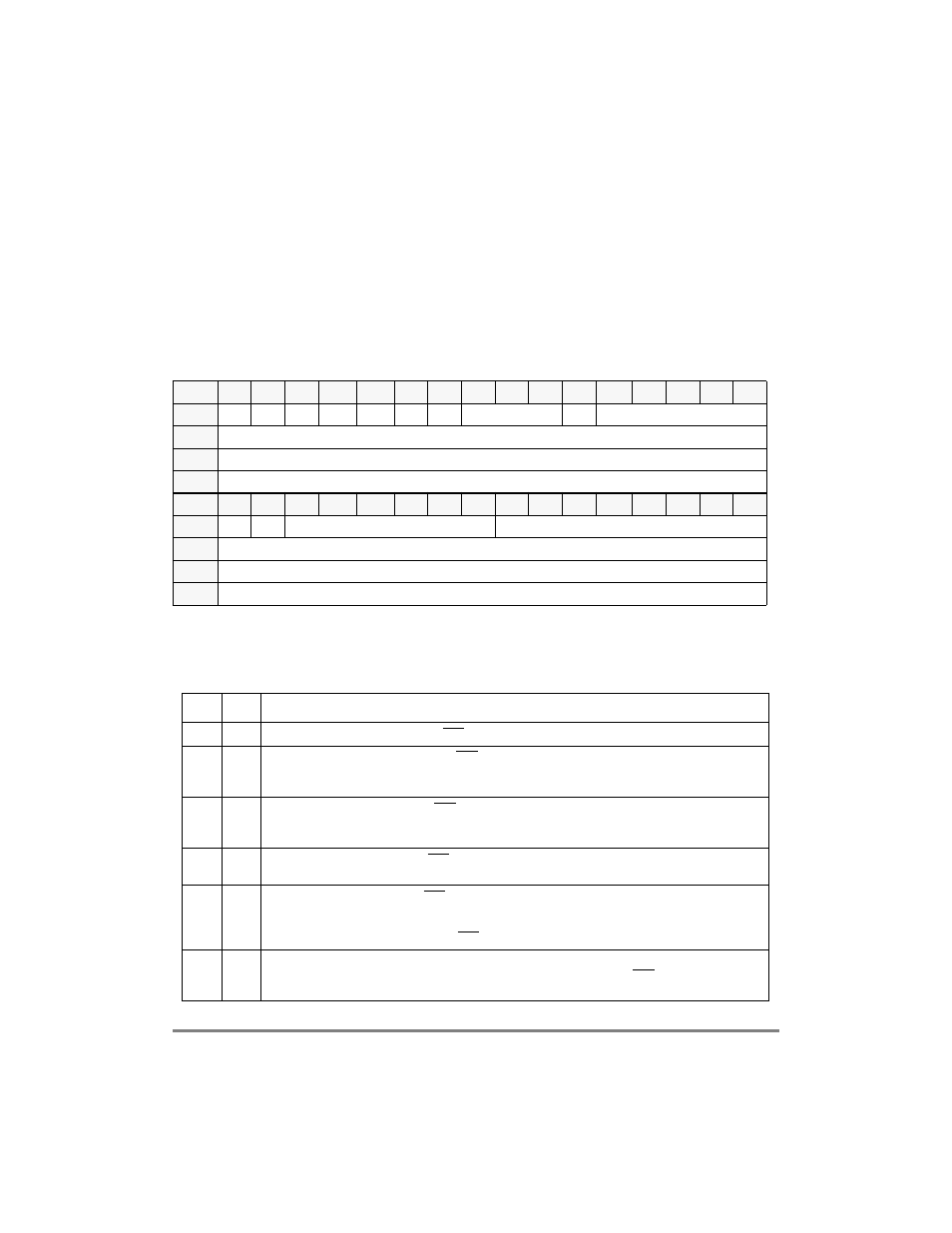

4.3.2.10 60x Bus Transfer Error Status and Control Register 1

(TESCR1)

The 60x bus transfer error status and control register 1 (TESCR1) is shown in Figure 4-31.

Table 4-15 describes TESCR1 Þelds.

Bits

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Field

BM

ISBE PAR ECC2 ECC1

WP

EXT

TC

Ñ

TT

Reset

0000_0000_0000_0000

R/W

R/W

Addr

Bits

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

Field

Ñ

DMD

Ñ

ECNT

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x10042

Figure 4-31. The 60x Bus Transfer Error Status and Control Register 1 (TESCR1)

Table 4-15. TESCR1 Field Descriptions

Bits

Name

Description

0

BM

60x bus monitor time-out. Set when TEA is asserted due to the 60x bus monitor time-out.

1

ISBE

Internal space bus error. Indicates that TEA was asserted due to error on a transaction to MPC8260Õs

internal memory space. TESCR2[REGS, DPR] indicate which of MPC8260Õs internal slaves caused

the error.

2

PAR

60x bus parity error. Indicates that TEA was asserted due to parity error on the 60x bus. TESCR2[PB]

indicates which byte lane caused the error; TESCR2[BNK] indicates which memory controller bank

was accessed.

3

ECC2 Double ECC error. Indicates that TEA was asserted due to double ECC error on the 60x bus.

TESCR2[BNK] indicates which memory controller bank was accessed.

4

ECC1 Single ECC error. Indicates that TEA was asserted due to single bit ECC error on the 60x bus.

TESCR2[BNK] indicates which memory controller bank was accessed. Single-bit errors are usually

Þxed by the ECC logic. However, if the ECC counter (ECNT) has reached its maximum value, all

single-bit errors cause the assertion of TEA.

5

WP

Write protect error. Indicates that a write was attempted to a 60x bus memory region that was deÞned

as read-only in the memory controller. Note that this alone does not cause TEA assertion. Usually, in

this case, the bus monitor will time-out.