1 features, 2 smc uart channel transmission process, Features -11 – Motorola MPC8260 User Manual

Page 707: Smc uart channel transmission process -11, Smc uart frame format -11

MOTOROLA

Chapter 26. Serial Management Controllers (SMCs)

26-11

Part IV. Communications Processor Module

However, SMCs allow a data length of up to 14 bits; SCCs support up to 8 bits.

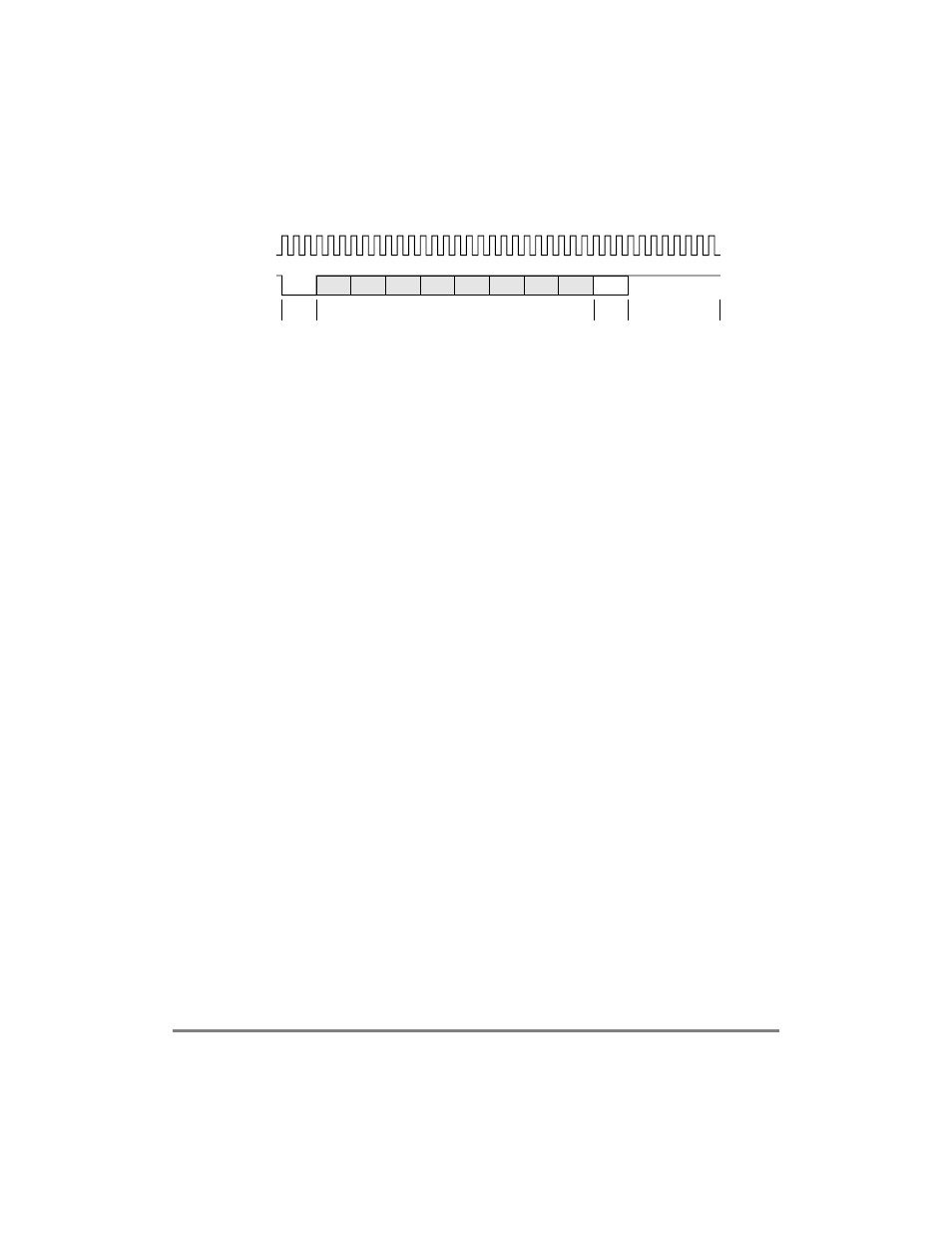

Figure 26-5. SMC UART Frame Format

26.3.1 Features

The following list summarizes the main features of the SMC in UART mode:

¥

Flexible message-oriented data structure

¥

Programmable data length (5Ð14 bits)

¥

Programmable 1 or 2 stop bits

¥

Even/odd/no parity generation and checking

¥

Frame error, break, and idle detection

¥

Transmit preamble and break sequences

¥

Received break character length indication

¥

Continuous receive and transmit modes

26.3.2 SMC UART Channel Transmission Process

The UART transmitter is designed to work with almost no intervention from the core. When

the core enables the SMC transmitter, it starts sending idles. The SMC immediately polls

the Þrst BD in the transmit channel BD table and once every character time after that,

depending on character length. When there is a message to transmit, the SMC fetches data

from memory and starts sending the message.

When a BD data is completely written to the transmit FIFO, the SMC writes the message

status bits into the BD and clears R. An interrupt is issued if the I bit in the BD is set. If the

next TxBD is ready, the data from its buffer is appended to the previous data and sent over

the transmit signal without any gaps between buffers. If the next TxBD is not ready, the

SMC starts sending idles and waits for the next TxBD to be ready.

By appropriately setting the I bit in each BD, interrupts can be generated after each buffer,

a speciÞc buffer, or each block is sent. The SMC then proceeds to the next BD. If the CM

bit is set in the TxBD, the R bit is not cleared, allowing a buffer to be automatically resent

next time the CP accesses this buffer. For instance, if a single TxBD is initialized with the

CM and W bits set, the buffer is sent continuously until R is cleared in the BD.

SMCLK

SMTXD

16x

Start

Bit

Parity

Bit

(Optional)

5 to 14 Data Bits with the

Least Significant Bit First

1 or 2

Stop Bits

(not to scale)