Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 92

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

92 of 792

NXP Semiconductors

UM10237

Chapter 5: LPC24XX External Memory Controller (EMC)

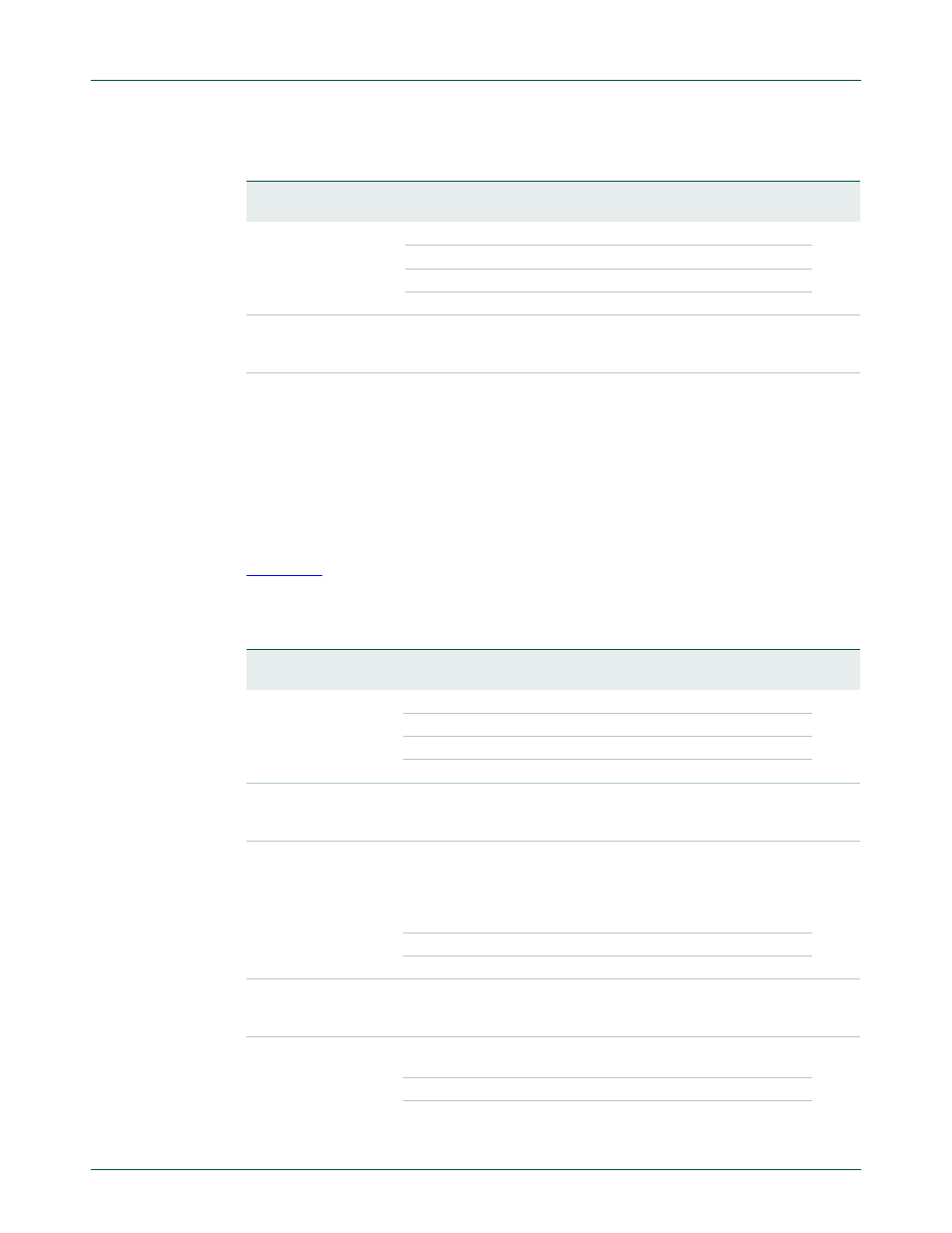

10.21 Static Memory Configuration registers (EMCStaticConfig0-3 -

0xFFE0 8200, 220, 240, 260)

The EMCStaticConfig0-3 registers configure the static memory configuration. It is

recommended that these registers are modified during system initialization, or when there

are no current or outstanding transactions. This can be ensured by waiting until the EMC

is idle, and then entering low-power, or disabled mode. These registers are accessed with

one wait state.

shows the bit assignments for the EMCStaticConfig0-3 registers. Note that

synchronous burst mode memory devices are not supported.

9:8

CAS latency

(CAS)

00

Reserved.

11

01

One CCLK cycle.

10

Two CCLK cycles.

11

Three CCLK cycles (POR reset value).

31:10 -

-

Reserved, user software should not write ones to

reserved bits. The value read from a reserved bit is not

defined.

NA

Table 88.

Dynamic Memory RAS & CAS Delay registers (EMCDynamicRasCas0-3 - address

0xFFE0 8104, 0xFFE0 8124, 0xFFE0 8144, 0xFFE0 8164) bit description

Bit

Symbol

Value Description

Reset

Value

Table 89.

Static Memory Configuration registers (EMCStaticConfig0-3 - address

0xFFE0 8200, 0xFFE0 8220, 0xFFE0 8240, 0xFFE0 8260) bit description

Bit

Symbol

Value Description

Reset

Value

1:0

Memory width

(MW)

00

8 bit (POR reset value).

0

01

16 bit.

10

32 bit.

11

Reserved.

2

-

-

Reserved, user software should not write ones to

reserved bits. The value read from a reserved bit is not

defined.

NA

3

Page mode

(PM)

In page mode the EMC can burst up to four external

accesses. Therefore devices with asynchronous page

mode burst four or higher devices are supported.

Asynchronous page mode burst two devices are not

supported and must be accessed normally.

0

0

Disabled (POR reset value).

1

Async page mode enabled (page length four).

5:4

-

-

Reserved, user software should not write ones to

reserved bits. The value read from a reserved bit is not

defined.

NA

6

Chip select

polarity (PC)

The value of the chip select polarity on power-on reset is

0.

0

0

Active LOW chip select.

1

Active HIGH chip select.