Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 51

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

51 of 792

NXP Semiconductors

UM10237

Chapter 4: LPC24XX Clocking and power control

3.2.6 PLL Status register (PLLSTAT - 0xE01F C088)

The read-only PLLSTAT register provides the actual PLL parameters that are in effect at

the time it is read, as well as the PLL status. PLLSTAT may disagree with values found in

PLLCON and PLLCFG because changes to those registers do not take effect until a

proper PLL feed has occurred (see

Section 4–3.2.9 “PLL Feed register (PLLFEED -

).

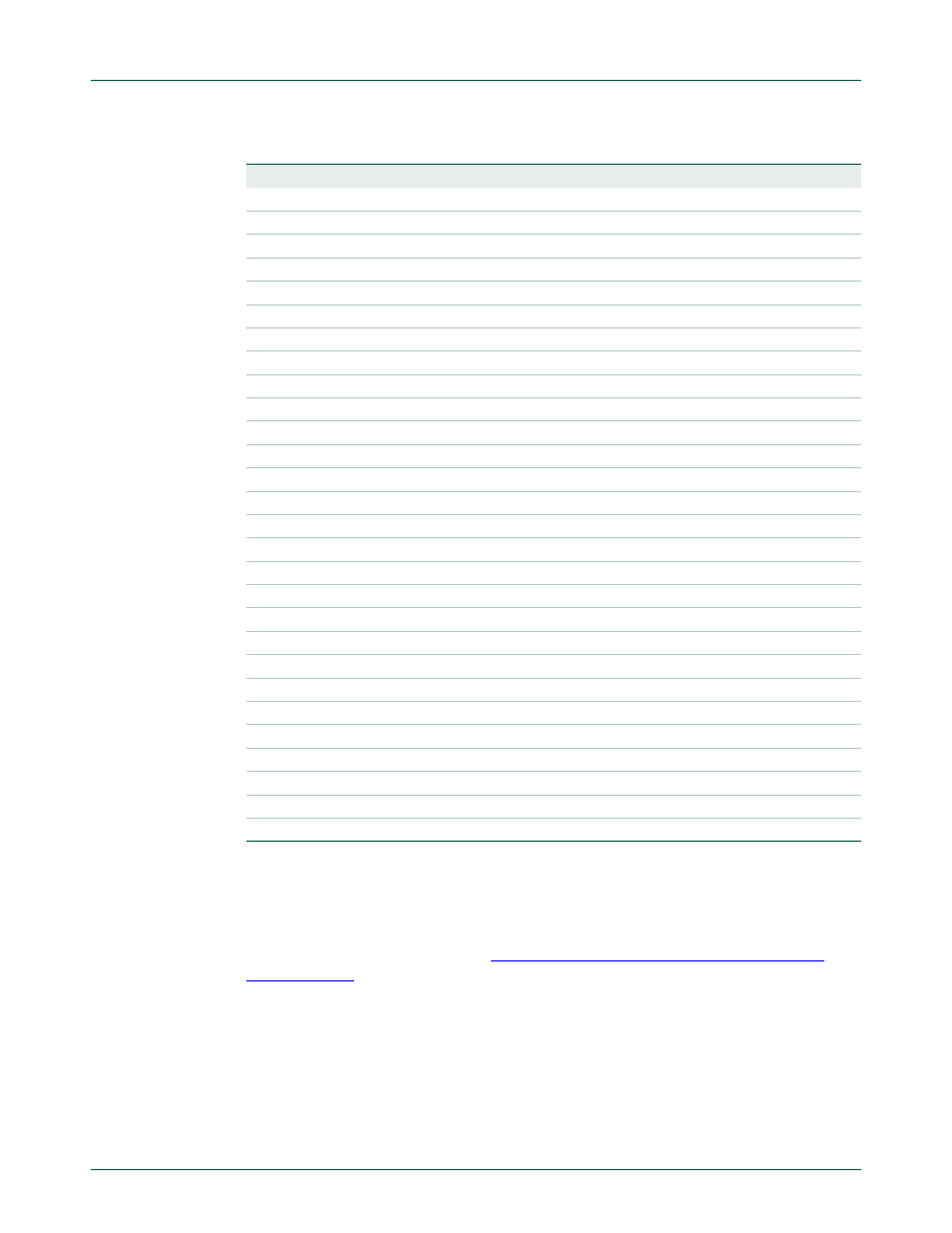

13672 2

448.0041

13733 2

450.0029

13733 3

300.0020

13916 2

455.9995

14099 2

461.9960

14420 3

315.0097

14648 2

479.9857

15381 2

504.0046

15381 3

336.0031

15564 3

340.0008

15625 2

512.0000

15869 2

519.9954

16113 2

527.9908

16479 3

359.9892

17578 3

383.9973

18127 3

395.9904

18311 3

400.0099

19226 3

419.9984

19775 3

431.9915

20508 3

448.0041

20599 3

449.9920

20874 3

455.9995

21149 3

462.0070

21973 3

480.0075

23071 3

503.9937

23438 3

512.0109

23804 3

520.0063

24170 3

528.0017

Table 46.

Multiplier values for a 32 kHz oscillator

Multiplier (M)

Pre-divide (N)

F

CCO