Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 229

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

229 of 792

NXP Semiconductors

UM10237

Chapter 11: LPC24XX Ethernet

All bits can be written and read. The Tx/RxReset bits are write only, reading will return a 0.

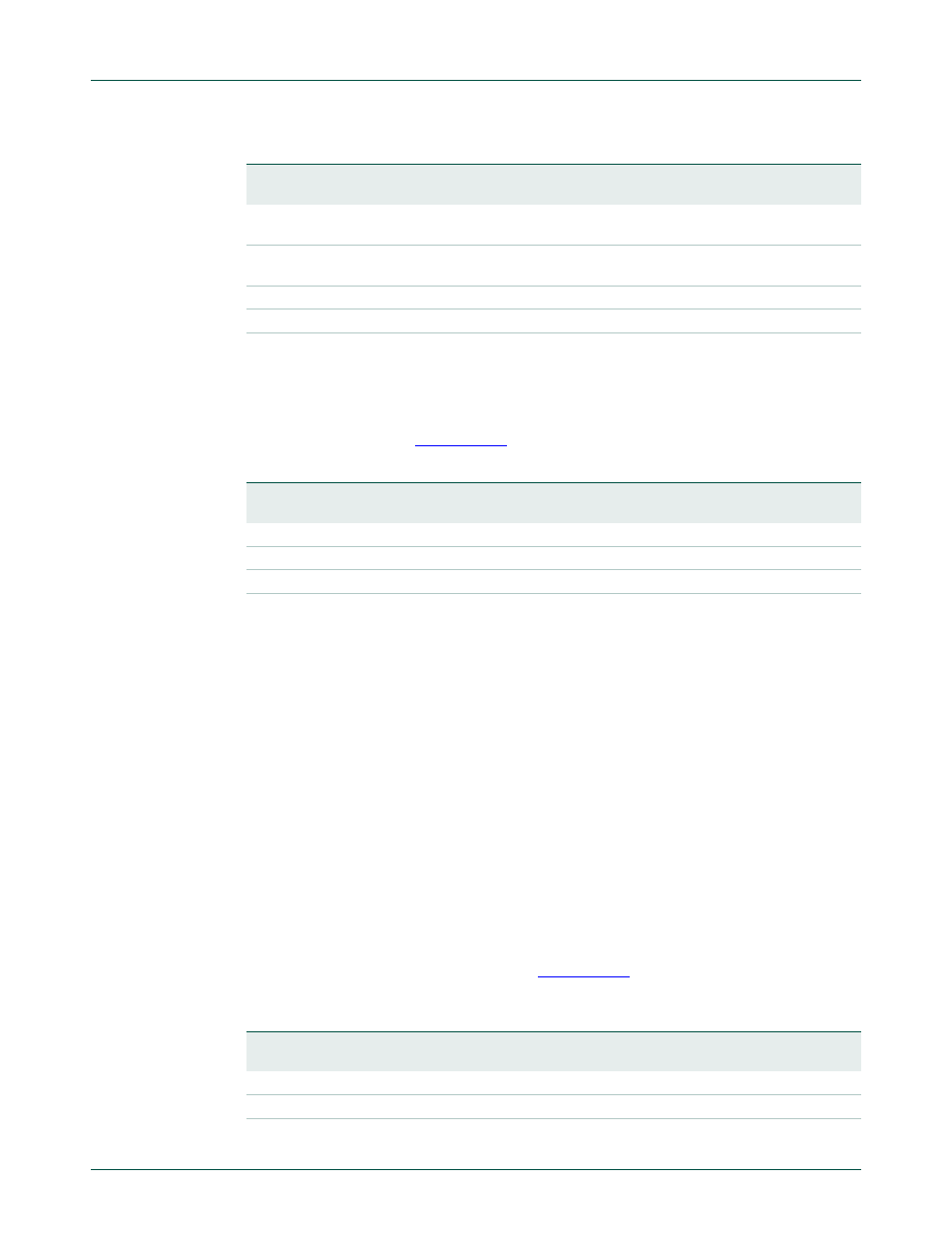

7.2.2 Status Register (Status - 0xFFE0 0104)

The Status register (Status) is a Read Only register with an address of 0xFFE0 0104. Its

bit definition is shown in

.

The values represent the status of the two channels/datapaths. When the status is 1, the

channel is active, meaning:

•

It is enabled and the Rx/TxEnable bit is set in the Command register or it just got

disabled while still transmitting or receiving a frame.

•

Also, for the transmit channel, the transmit queue is not empty

i.e. ProduceIndex != ConsumeIndex.

•

Also, for the receive channel, the receive queue is not full

i.e. ProduceIndex != ConsumeIndex - 1.

The status transitions from active to inactive if the channel is disabled by a software reset

of the Rx/TxEnable bit in the Command register and the channel has committed the status

and data of the current frame to memory. The status also transitions to inactive if the

transmit queue is empty or if the receive queue is full and status and data have been

committed to memory.

7.2.3 Receive Descriptor Base Address Register (RxDescriptor - 0xFFE0 0108)

The Receive Descriptor base address register (RxDescriptor) has an address of

0xFFE0 0108. Its bit definition is shown in

.

8

TxFlowControl

Enable IEEE 802.3 / clause 31 flow control sending pause

frames in full duplex and continuous preamble in half duplex.

0

9

RMII

When set to ’1’, RMII mode is selected; if ’0’, MII mode is

selected.

0

10

FullDuplex

When set to ’1’, indicates full duplex operation.

0

31:11

-

Unused

0x0

Table 206. Command register (Command - address 0xFFE0 0100) bit description

Bit

Symbol

Function

Reset

value

Table 207. Status register (Status - address 0xFFE0 0104) bit description

Bit

Symbol

Function

Reset

value

0

RxStatus If 1, the receive channel is active. If 0, the receive channel is inactive.

0

1

TxStatus

If 1, the transmit channel is active. If 0, the transmit channel is inactive. 0

31:2

-

Unused

0x0

Table 208. Receive Descriptor Base Address register (RxDescriptor - address 0xFFE0 0108)

bit description

Bit

Symbol

Function

Reset

value

1:0

-

Fixed to ’00’

-

31:2

RxDescriptor

MSBs of receive descriptor base address.

0x0