16 interrupt handling, Section 15–7.16, Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 410

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

410 of 792

NXP Semiconductors

UM10237

Chapter 15: LPC24XX USB OTG controller

7.15 I2C Clock Low Register (I2C_CLKLO - 0xFFE0 C310)

The CLK register holds a terminal count for counting 48 MHz clock cycles to create the

low period of the slower I

2

C serial clock, SCL.

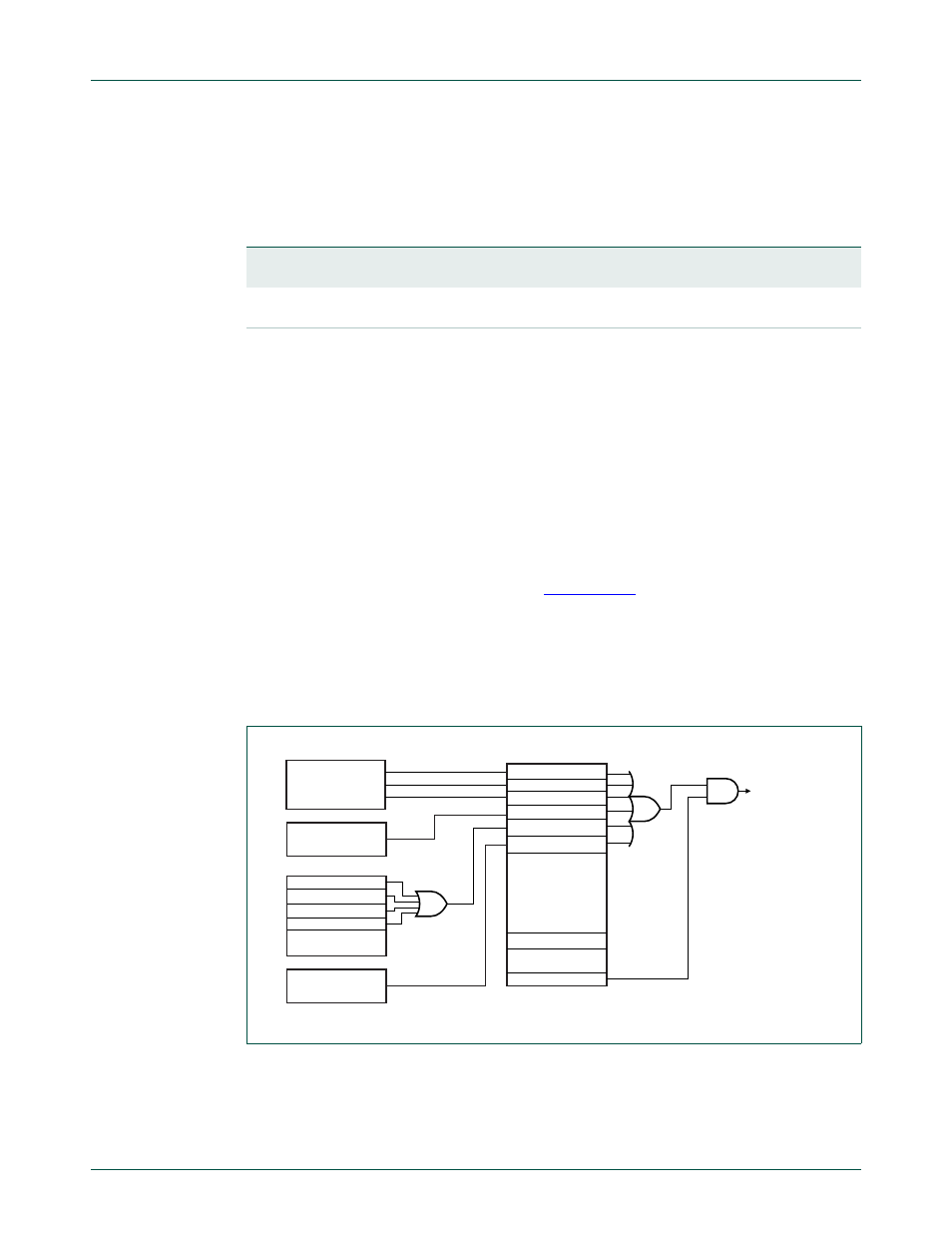

7.16 Interrupt handling

The interrupts set in the OTGIntSt register are set and cleared during HNP switching. All

OTG related interrupts, if enabled, are routed to the USB_OTG_INT bit in the USBIntSt

register.

I2C related interrupts are set in the I2C_STS register and routed, if enabled by I2C_CTL,

to the USB_I2C_INT bit.

For more details on the interrupts created by device controller, see the USB device

chapter. For interrupts created by the host controllers, see the OHCI specification.

The EN_USB_INTS bit in the USBIntSt register enables the routing of any of the USB

related interrupts to the VIC controller (see

Remark: During the HNP switching between host and device with the OTG stack active,

an action may raise several levels of interrupts. It is advised to let the OTG stack initiate

any actions based on interrupts and ignore device and host level interrupts. This means

that during HNP switching, the OTG stack provides the communication to the host and

device controllers.

Table 375. I2C_CLKLO register (I2C_CLKLO - address 0xFFE0 C310) bit description

Bit

Symbol

Description

Reset

Value

7:0

CDLO

Clock divisor low. This value is the number of 48 MHz

clocks the serial clock (SCL) will be low.

0xB9

Fig 58. USB OTG interrupt handling

USB_INT_REQ_HP

USB_INT_REQ_LP

USB_INT_REQ_DMA

EN_USB_INTS

to VIC

channel #22

USB_HOST_INT

USB_OTG_INT

USB_I2C_INT

USB_NEED_CLOCK

USBIntSt

USB DEVICE

INTERRUPTS

USB HOST

INTERRUPTS

OTGIntSt

TMR

REMOVE_PU

HNP_SUCCESS

HNP_FAILURE

USB I2C

INTERRUPTS