Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 221

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

221 of 792

NXP Semiconductors

UM10237

Chapter 11: LPC24XX Ethernet

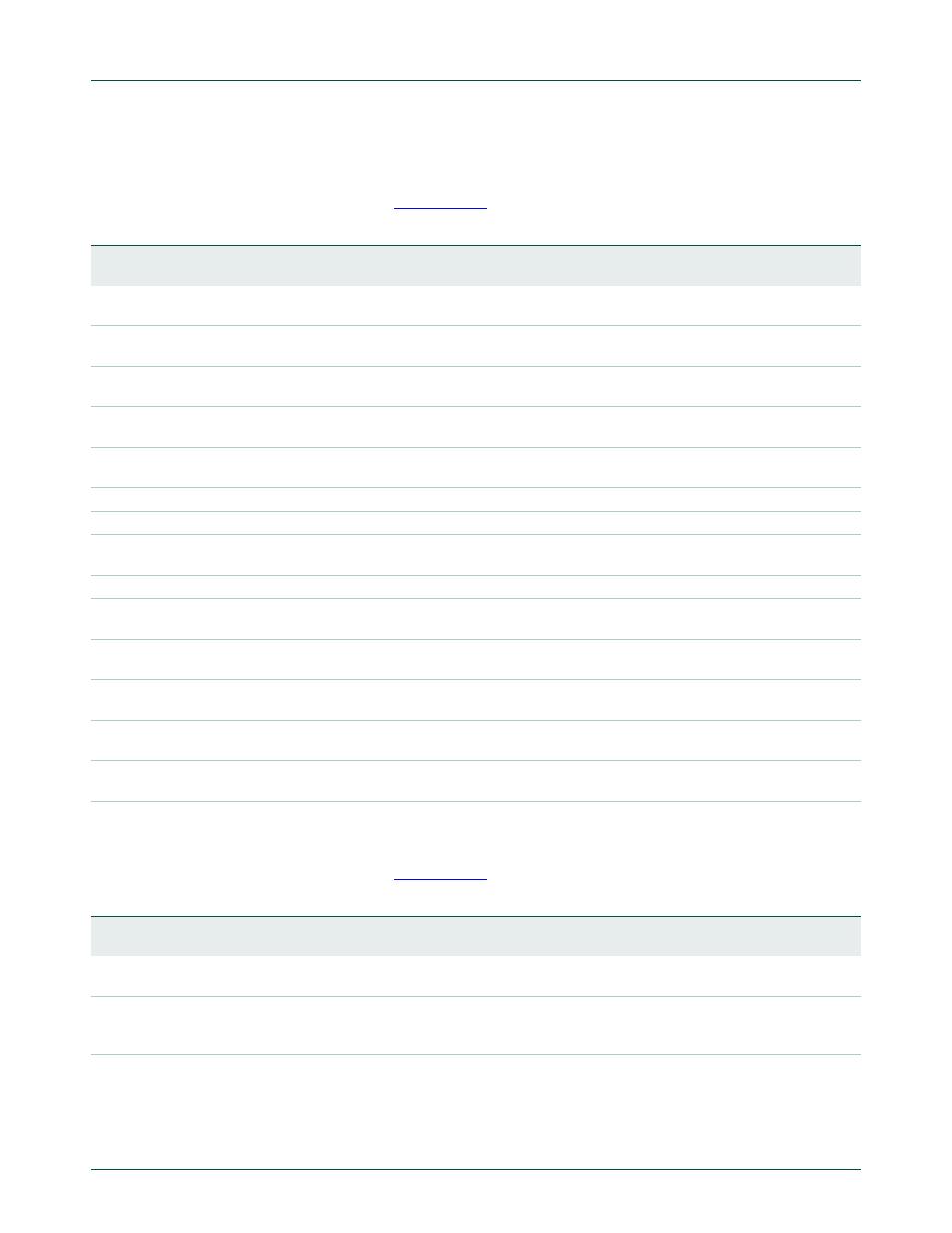

7.1.1 MAC Configuration Register 1 (MAC1 - 0xFFE0 0000)

The MAC configuration register 1 (MAC1) has an address of 0xFFE0 0000. Its bit

definition is shown in

7.1.2 MAC Configuration Register 2 (MAC2 - 0xFFE0 0004)

The MAC configuration register 2 (MAC2) has an address of 0xFFE0 0004. Its bit

definition is shown in

Table 187. MAC Configuration register 1 (MAC1 - address 0xFFE0 0000) bit description

Bit

Symbol

Function

Reset

value

0

RECEIVE ENABLE

Set this to allow receive frames to be received. Internally the MAC synchronizes

this control bit to the incoming receive stream.

0

1

PASS ALL RECEIVE

FRAMES

When enabled (set to ’1’), the MAC will pass all frames regardless of type (normal

vs. Control). When disabled, the MAC does not pass valid Control frames.

0

2

RX FLOW CONTROL When enabled (set to ’1’), the MAC acts upon received PAUSE Flow Control

frames. When disabled, received PAUSE Flow Control frames are ignored.

0

3

TX FLOW CONTROL

When enabled (set to ’1’), PAUSE Flow Control frames are allowed to be

transmitted. When disabled, Flow Control frames are blocked.

0

4

LOOPBACK

Setting this bit will cause the MAC Transmit interface to be looped back to the MAC

Receive interface. Clearing this bit results in normal operation.

0

7:5

-

Unused

0x0

8

RESET TX

Setting this bit will put the Transmit Function logic in reset.

0

9

RESET MCS / TX

Setting this bit resets the MAC Control Sublayer / Transmit logic. The MCS logic

implements flow control.

0

10

RESET RX

Setting this bit will put the Ethernet receive logic in reset.

0

11

RESET MCS / RX

Setting this bit resets the MAC Control Sublayer / Receive logic. The MCS logic

implements flow control.

0x0

13:12

-

Reserved. User software should not write ones to reserved bits. The value read

from a reserved bit is not defined.

0x0

14

SIMULATION RESET

Setting this bit will cause a reset to the random number generator within the

Transmit Function.

0

15

SOFT RESET

Setting this bit will put all modules within the MAC in reset except the Host

Interface.

1

31:16

-

Reserved. User software should not write ones to reserved bits. The value read

from a reserved bit is not defined.

0x0

Table 188. MAC Configuration register 2 (MAC2 - address 0xFFE0 0004) bit description

Bit

Symbol

Function

Reset

value

0

FULL-DUPLEX

When enabled (set to ’1’), the MAC operates in Full-Duplex mode. When disabled,

the MAC operates in Half-Duplex mode.

0

1

FRAME LENGTH

CHECKING

When enabled (set to ’1’), both transmit and receive frame lengths are compared to

the Length/Type field. If the Length/Type field represents a length then the check is

performed. Mismatches are reported in the StatusInfo word for each received frame.

0

2

HUGE FRAME

ENABLE

When enabled (set to ’1’), frames of any length are transmitted and received.

0