Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 311

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

311 of 792

NXP Semiconductors

UM10237

Chapter 12: LPC24XX LCD controller

Optionally, the value may be changed mid-frame to create double-buffered video displays.

These registers are copied to the corresponding current registers at each LCD vertical

synchronization. This event causes the LNBU bit and an optional interrupt to be

generated. The interrupt can be used to reprogram the base address when generating

double-buffered video.

The contents of the LCD_LPBASE register are described in

.

7.8 LCD Control register (LCD_CTRL, RW - 0xFFE1 0018)

The LCD_CTRL register controls the LCD operating mode and the panel pixel

parameters.

The contents of the LCD_CTRL register are described in

.

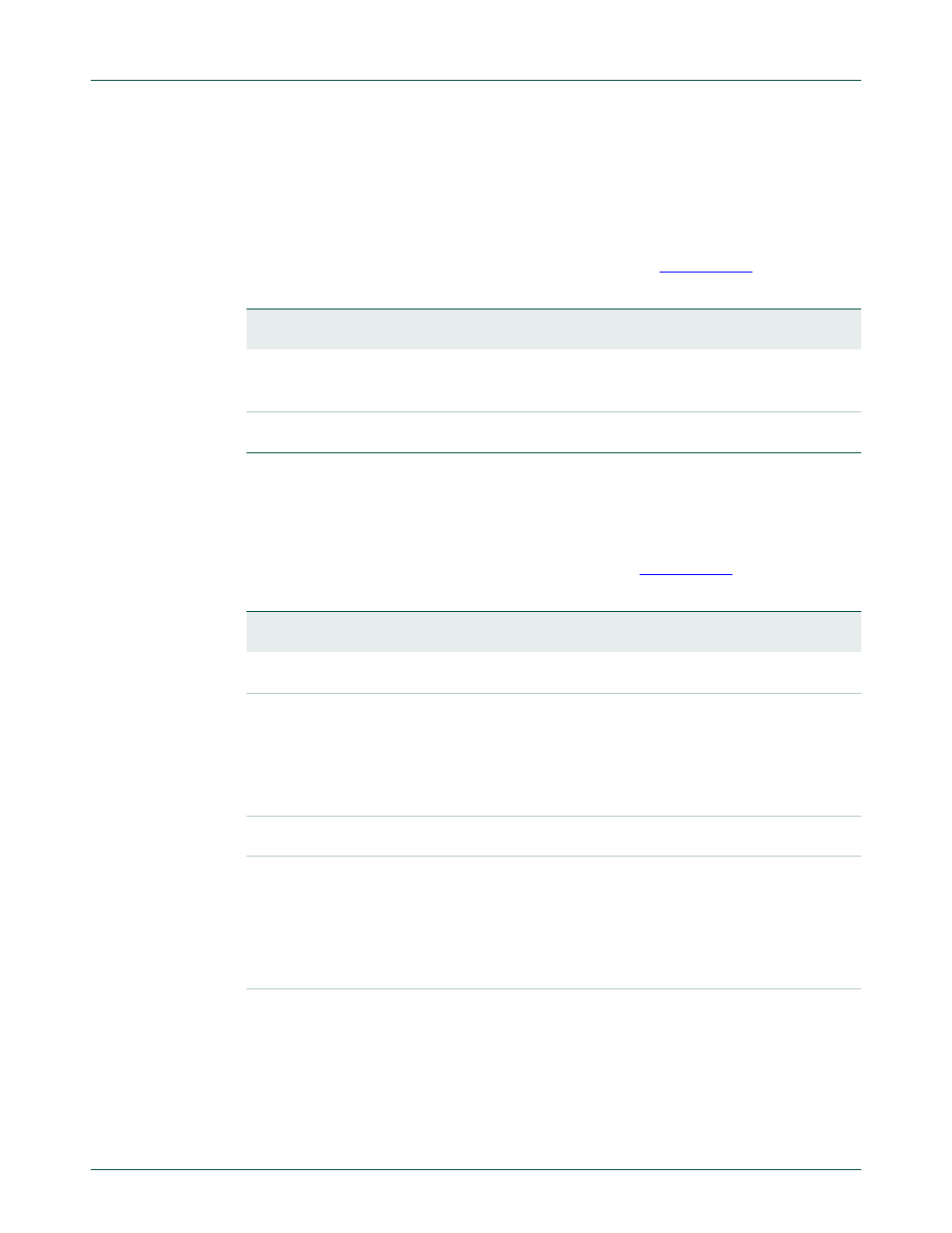

Table 266. Lower Panel Frame Base register (LCD_LPBASE, RW - 0xFFE1 0014)

Bits

Function

Description

Reset

value

31:3

LCDLPBASE

LCD lower panel base address.

This is the start address of the lower panel frame data in memory

and is doubleword aligned.

0x0

2:0

reserved

Reserved, user software should not write ones to reserved bits.

The value read from a reserved bit is not defined.

-

Table 267. LCD Control register (LCD_CTRL, RW - 0xFFE1 0018)

Bits

Function

Description

Reset

value

31:17

reserved

Reserved, user software should not write ones to reserved bits.

The value read from a reserved bit is not defined.

-

16

WATERMARK LCD DMA FIFO watermark level.

Controls when DMA requests are generated:

0 = An LCD DMA request is generated when either of the DMA

FIFOs have four or more empty locations.

1 = An LCD DMA request is generated when either of the DMA

FIFOs have eight or more empty locations.

0x0

15:14

reserved

Reserved, user software should not write ones to reserved bits.

The value read from a reserved bit is not defined.

-

13:12

LcdVComp

LCD Vertical Compare Interrupt.

Generate VComp interrupt at:

00 = start of vertical synchronization.

01 = start of back porch.

10 = start of active video.

11 = start of front porch.

0x0

11

LcdPwr

LCD power enable.

0 = power not gated through to LCD panel and LCDV[23:0]

signals disabled, (held LOW).

1 = power gated through to LCD panel and LCDV[23:0] signals

enabled, (active).

See LCD power-up and power-down sequence for details on

LCD power sequencing.

0x0