Table 4–57, Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 59

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

59 of 792

NXP Semiconductors

UM10237

Chapter 4: LPC24XX Clocking and power control

[1]

For PCLK_RTC only, the value ’01’ is illegal. Do not write ’01’ to the PCLK_RTC. Attempting to write ’01’

results in the previous value being unchanged.

[2]

PCLK_CAN1/2 must be set to the same value as PCLK_ACF.

11:10

PCLK_PWM0

Peripheral clock selection for PWM0.

00

13:12

PCLK_PWM1

Peripheral clock selection for PWM1.

00

15:14

PCLK_I2C0

Peripheral clock selection for I2C0.

00

17:16

PCLK_SPI

Peripheral clock selection for SPI.

00

19:18

PCLK_RTC

Peripheral clock selection for RTC.

00

21:20

PCLK_SSP1

Peripheral clock selection for SSP1.

00

23:22

PCLK_DAC

Peripheral clock selection for DAC.

00

25:24

PCLK_ADC

Peripheral clock selection for ADC.

00

27:26

PCLK_CAN1

Peripheral clock selection for CAN1.

00

29:28

PCLK_CAN2

Peripheral clock selection for CAN2.

00

31:30

PCLK_ACF

Peripheral clock selection for CAN filtering.

00

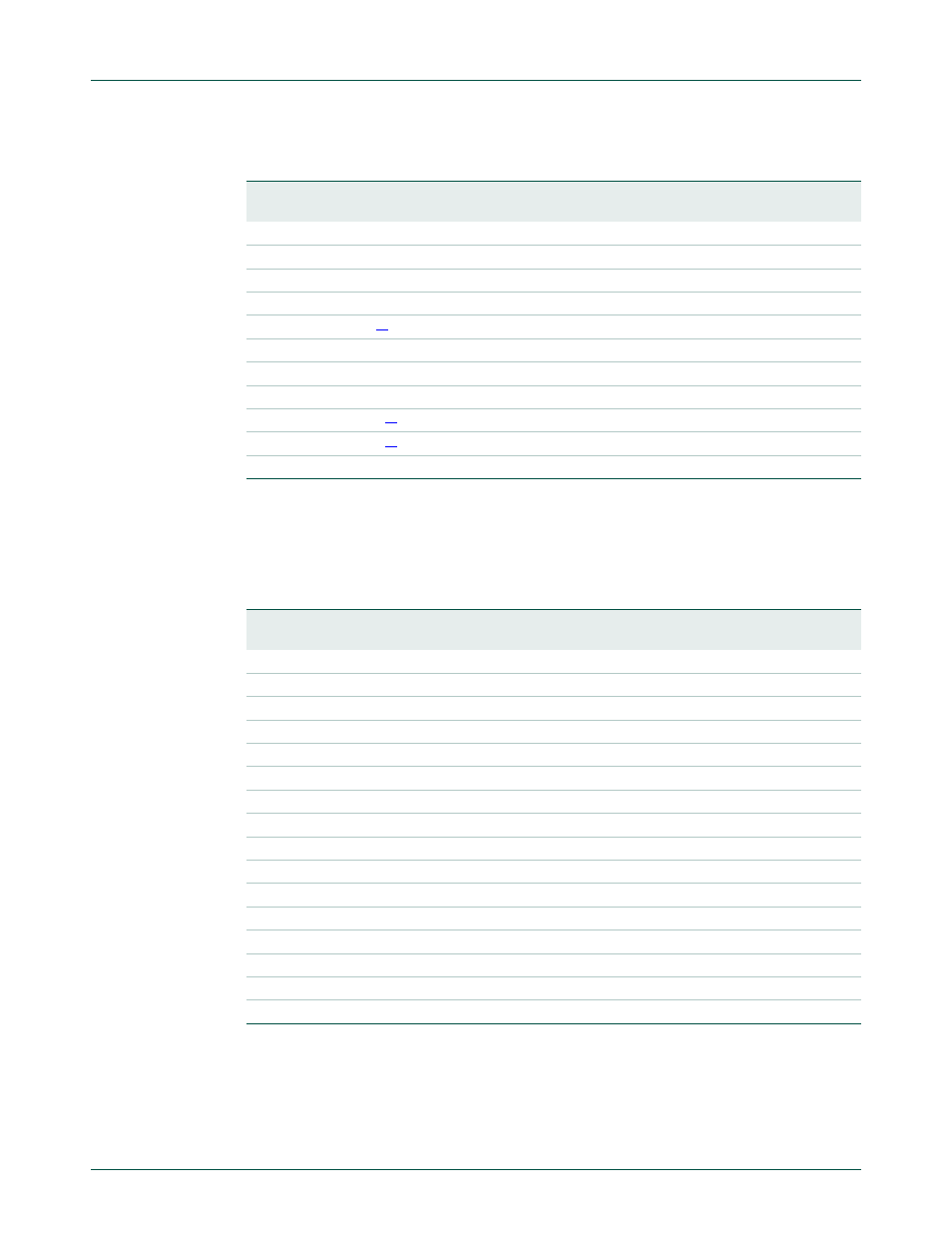

Table 57.

Peripheral Clock Selection register 1 (PCLKSEL1 - address 0xE01F C1AC) bit

description

Bit

Symbol

Description

Reset

value

1:0

PCLK_BAT_RAM

Peripheral clock selection for the battery supported RAM.

00

3:2

PCLK_GPIO

Peripheral clock selection for GPIOs.

00

5:4

PCLK_PCB

Peripheral clock selection for the Pin Connect block.

00

7:6

PCLK_I2C1

Peripheral clock selection for I2C1.

00

9:8

-

Unused, always read as 0.

00

11:10

PCLK_SSP0

Peripheral clock selection for SSP0.

00

13:12

PCLK_TIMER2

Peripheral clock selection for TIMER2.

00

15:14

PCLK_TIMER3

Peripheral clock selection for TIMER3.

00

17:16

PCLK_UART2

Peripheral clock selection for UART2.

00

19:18

PCLK_UART3

Peripheral clock selection for UART3.

00

21:20

PCLK_I2C2

Peripheral clock selection for I2C2.

00

23:22

PCLK_I2S

Peripheral clock selection for I2S.

00

25:24

PCLK_MCI

Peripheral clock selection for MCI.

00

27:26

-

Unused, always read as 0.

00

29:28

PCLK_SYSCON

Peripheral clock selection for the System Control block.

00

31:30

-

Unused, always read as 0.

00

Table 56.

Peripheral Clock Selection register 0 (PCLKSEL0 - address 0xE01F C1A8) bit

description

Bit

Symbol

Description

Reset

value