Table 16–380, Table 16–381, Table 16–382 – NXP Semiconductors LPC24XX UM10237 User Manual

Page 428: Nxp semiconductors

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

428 of 792

NXP Semiconductors

UM10237

Chapter 16: LPC24XX UART0/2/3

higher 8 bits of the divisor. A 0x0000 value is treated like a 0x0001 value as division by

zero is not allowed. The Divisor Latch Access Bit (DLAB) in UnLCR must be one in order

to access the UARTn Divisor Latches.

4.4 UARTn Interrupt Enable Register (U0IER - 0xE000 C004, U2IER -

0xE007 8004, U3IER - 0xE007 C004 when DLAB = 0)

The UnIER is used to enable the three UARTn interrupt sources.

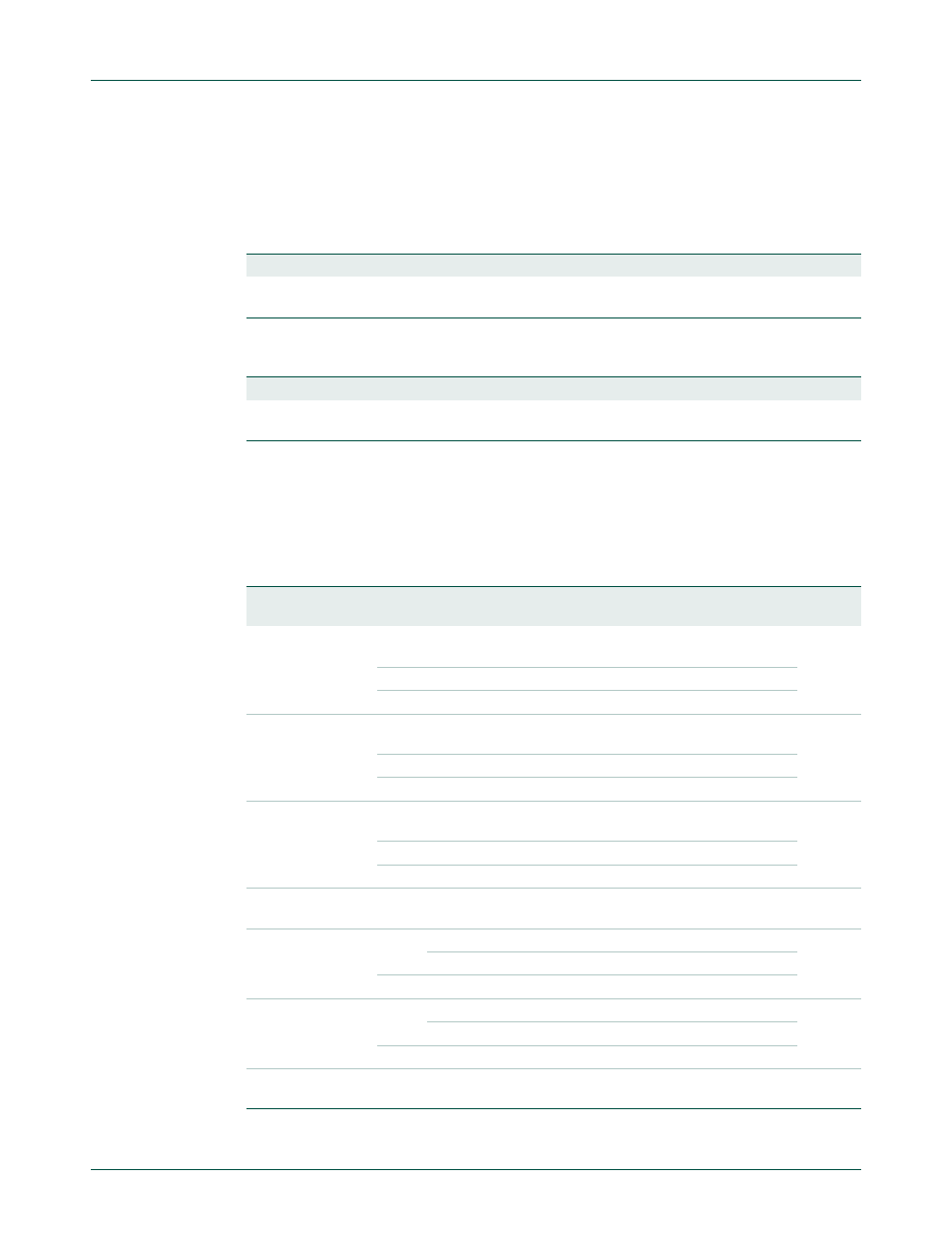

Table 380. UARTn Divisor Latch LSB Register (U0DLL - address 0xE000 C000,

U2DLL - 0xE007 8000, U3DLL - 0xE007 C000 when DLAB = 1) bit description

Bit

Symbol

Description

Reset Value

7:0

DLLSB

The UARTn Divisor Latch LSB Register, along with the UnDLM

register, determines the baud rate of the UARTn.

0x01

Table 381. UARTn Divisor Latch MSB Register (U0DLM - address 0xE000 C004,

U2DLM - 0xE007 8004, U3DLM - 0xE007 C004 when DLAB = 1) bit description

Bit

Symbol

Description

Reset Value

7:0

DLMSB

The UARTn Divisor Latch MSB Register, along with the U0DLL

register, determines the baud rate of the UARTn.

0x00

Table 382. UARTn Interrupt Enable Register (U0IER - address 0xE000 C004,

U2IER - 0xE007 8004, U3IER - 0xE007 C004 when DLAB = 0) bit description

Bit

Symbol

Value

Description

Reset

Value

0

RBR

Interrupt

Enable

enables the Receive Data Available interrupt for UARTn. It

also controls the Character Receive Time-out interrupt.

0

0

Disable the RDA interrupts.

1

Enable the RDA interrupts.

1

THRE

Interrupt

Enable

enables the THRE interrupt for UARTn. The status of this

can be read from UnLSR[5].

0

0

Disable the THRE interrupts.

1

Enable the THRE interrupts.

2

RX Line

Status

Interrupt

Enable

enables the UARTn RX line status interrupts. The status of

this interrupt can be read from UnLSR[4:1].

0

0

Disable the RX line status interrupts.

1

Enable the RX line status interrupts.

7:3

-

Reserved, user software should not write ones to reserved

bits. The value read from a reserved bit is not defined.

NA

8

ABEOIntEn

0

enables the end of auto-baud interrupt.

0

Disable End of Auto-baud Interrupt.

1

Enable End of Auto-baud Interrupt.

9

ABTOIntEn

0

enables the auto-baud time-out interrupt.

0

Disable Auto-baud Time-out Interrupt.

1

Enable Auto-baud Time-out Interrupt.

31:10 -

Reserved, user software should not write ones to reserved

bits. The value read from a reserved bit is not defined.

NA