Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 644

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

644 of 792

NXP Semiconductors

UM10237

Chapter 25: LPC24XX Pulse Width Modulator PWM0/PWM1

[1]

Reserved for PWM0.

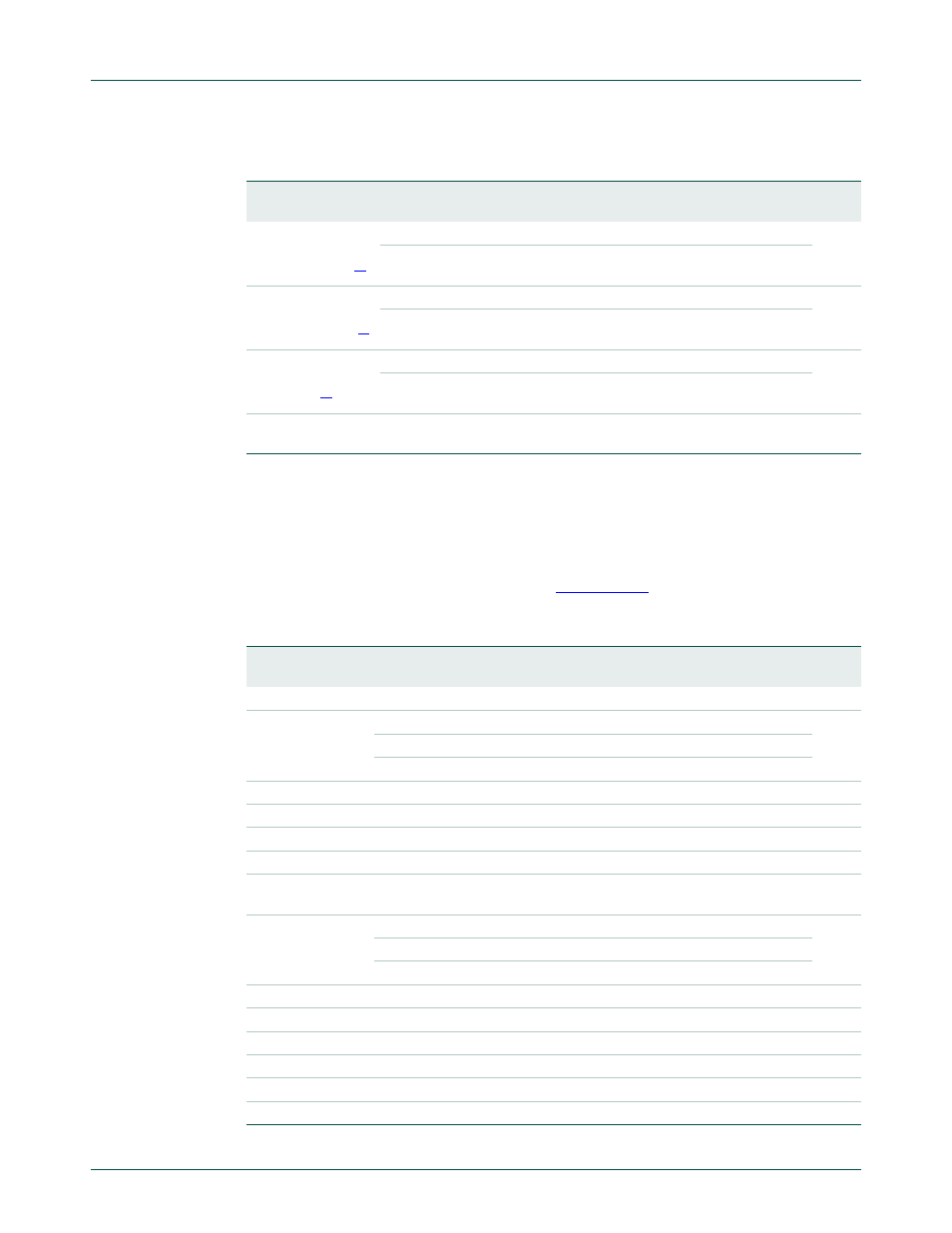

6.6 PWM Control Registers (PWM0PCR - 0xE001 404C and PWM1PCR

0xE001 804C)

The PWM Control registers are used to enable and select the type of each PWM channel.

The function of each of the bits are shown in

.

3

Capture on

PCAPn.1

rising edge

0

This feature is disabled.

0

1

A synchronously sampled rising edge on the PCAPn.1 input

will cause CR1 to be loaded with the contents of the TC.

4

Capture on

PCAPn.1

falling edge

0

This feature is disabled.

0

1

A synchronously sampled falling edge on PCAPn.1 will cause

CR1 to be loaded with the contents of TC.

5

Interrupt on

PCAPn.1

event

0

This feature is disabled.

0

1

A CR1 load due to a PCAPn.1 event will generate an

interrupt.

31:6 -

Reserved, user software should not write ones to reserved

bits. The value read from a reserved bit is not defined.

NA

Table 562: PWM Capture Control Register (PWM0CCR - address 0xE001 4028 and PWM1CCR

address 0xE001 8028) bit description

Bit

Symbol

Value Description

Reset

Value

Table 563: PWM Control Registers (PWMPCR - address 0xE001 404C and PWM1PCR

address 0xE001 804C) bit description

Bit

Symbol

Value Description

Reset

Value

1:0

Unused

Unused, always zero.

NA

2

PWMSEL2

PWM2 output single/double edge mode control.

0

1

Double edge controlled mode is selected.

0

Single edge controlled mode is selected.

3

PWMSEL3

1

PWM3 output edge control. See PWMSEL2 for details.

0

4

PWMSEL4

1

PWM4 output edge control. See PWMSEL2 for details.

0

5

PWMSEL5

1

PWM5 output edge control. See PWMSEL2 for details.

0

6

PWMSEL6

1

PWM6 output edge control. See PWMSEL2 for details.

0

8:7

-

Reserved, user software should not write ones to reserved

bits. The value read from a reserved bit is not defined.

NA

9

PWMENA1

The PWM1 output enable control.

0

0

The PWM output is disabled.

1

The PWM output is enabled.

10

PWMENA2

The PWM2 output enable control. See PWMENA1 for details. 0

11

PWMENA3

The PWM3 output enable control. See PWMENA1 for details. 0

12

PWMENA4

The PWM4 output enable control. See PWMENA1 for details. 0

13

PWMENA5

The PWM5 output enable control. See PWMENA1 for details. 0

14

PWMENA6

The PWM6 output enable control. See PWMENA1 for details. 0

31:15 Unused

Unused, always zero.

NA