2 address register i2addr, 3 comparator, 4 shift register i2dat – NXP Semiconductors LPC24XX UM10237 User Manual

Page 579: 5 arbitration and synchronization logic, Nxp semiconductors

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

579 of 792

NXP Semiconductors

UM10237

Chapter 22: LPC24XX I

2

C interfaces I

2

C0/1/2

7.2 Address Register I2ADDR

This register may be loaded with the 7 bit slave address (7 most significant bits) to which

the I

2

C block will respond when programmed as a slave transmitter or receiver. The LSB

(GC) is used to enable general call address (0x00) recognition.

7.3 Comparator

The comparator compares the received 7 bit slave address with its own slave address (7

most significant bits in I2ADR). It also compares the first received 8 bit byte with the

general call address (0x00). If an equality is found, the appropriate status bits are set and

an interrupt is requested.

7.4 Shift register I2DAT

This 8 bit register contains a byte of serial data to be transmitted or a byte which has just

been received. Data in I2DAT is always shifted from right to left; the first bit to be

transmitted is the MSB (bit 7) and, after a byte has been received, the first bit of received

data is located at the MSB of I2DAT. While data is being shifted out, data on the bus is

simultaneously being shifted in; I2DAT always contains the last byte present on the bus.

Thus, in the event of lost arbitration, the transition from master transmitter to slave

receiver is made with the correct data in I2DAT.

7.5 Arbitration and synchronization logic

In the master transmitter mode, the arbitration logic checks that every transmitted logic 1

actually appears as a logic 1 on the I

2

C bus. If another device on the bus overrules a logic

1 and pulls the SDA line low, arbitration is lost, and the I

2

C block immediately changes

from master transmitter to slave receiver. The I

2

C block will continue to output clock

pulses (on SCL) until transmission of the current serial byte is complete.

Arbitration may also be lost in the master receiver mode. Loss of arbitration in this mode

can only occur while the I

2

C block is returning a “not acknowledge: (logic 1) to the bus.

Arbitration is lost when another device on the bus pulls this signal LOW. Since this can

occur only at the end of a serial byte, the I

2

C block generates no further clock pulses.

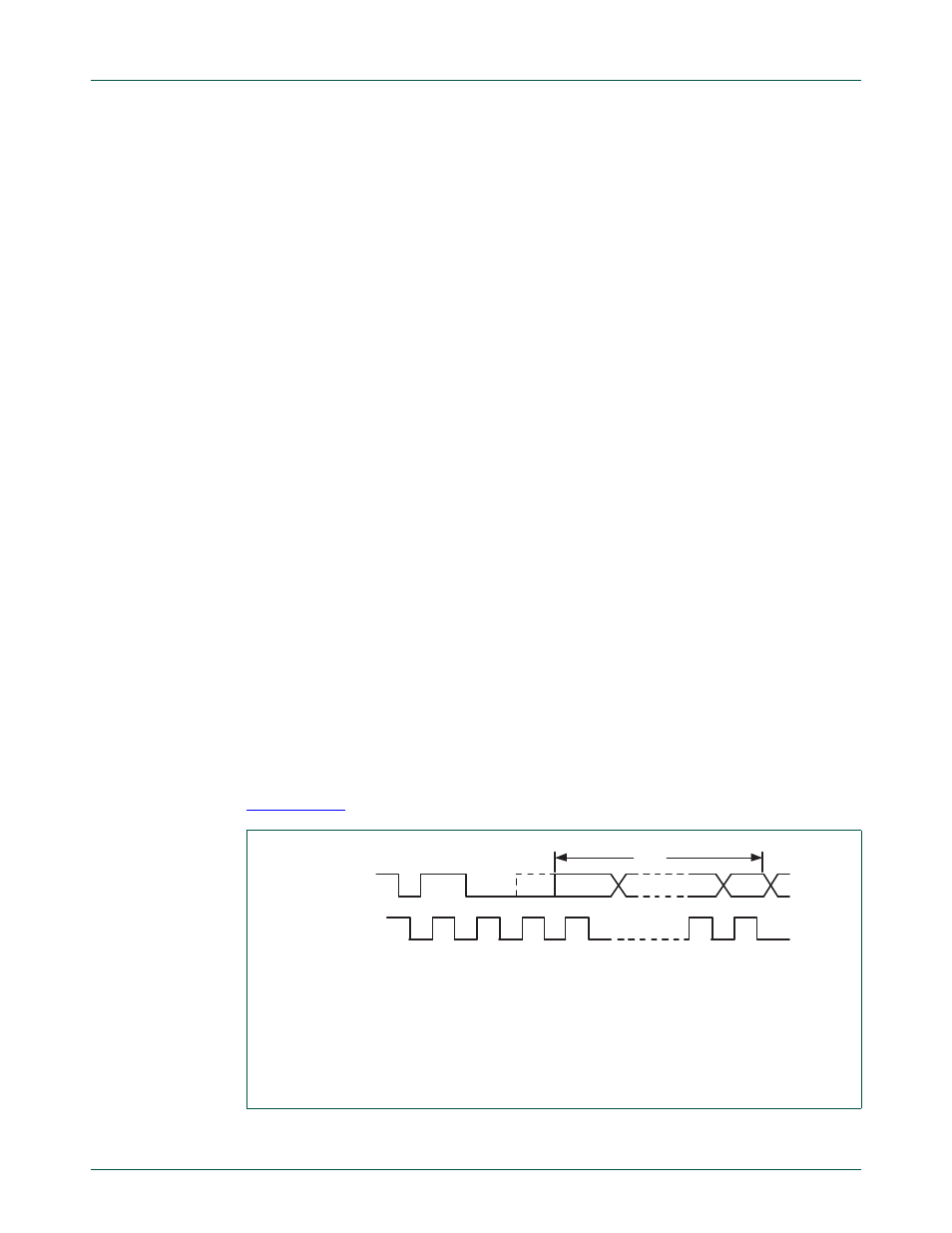

shows the arbitration procedure.

(1) A device transmits serial data.

(2) Another device overrules a logic 1 (dotted line), transmitted by this I

2

C master, by pulling the SDA

line low. Arbitration is lost, and this I

2

C enters Slave Receiver mode.

(3) This I

2

C is in Slave Receiver mode but still generates clock pulses until the current byte has been

transmitted. This I

2

C will not generate clock pulses for the next byte. Data on SDA originates from

the new master once it has won arbitration.

Fig 118. Arbitration procedure

SDA line

SCL line

1

2

3

4

8

9

ACK

(1)

(2)

(1)

(3)