3 rtc oscillator, Register description, Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 45

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

45 of 792

NXP Semiconductors

UM10237

Chapter 4: LPC24XX Clocking and power control

register) so that software can determine when the oscillator is running and stable. At that

point, software can control switching to the main oscillator as a clock source. Prior to

starting the main oscillator, a frequency range must be selected by configuring the

OSCRANGE bit in the SCS register.

2.2.1 XTAL1 input

The input voltage to the on-chip oscillators is limited to 1.8 V. If the oscillator is driven by a

clock in slave mode, it is recommended that the input be coupled through a capacitor with

C

i

= 100 pF. To limit the input voltage to the specified range, choose an additional

capacitor to ground C

g

which attenuates the input voltage by a factor C

i

/(C

i

+ C

g

), see

. In slave mode, a minimum of 200 mV(RMS) is needed.

2.2.2 Printed Circuit Board (PCB) layout guidelines

The crystal should be connected on the PCB as close as possible to the oscillator input

and output pins of the chip. Take care that the load capacitors C

x1

and C

x2

, and C

x3

in

case of third overtone crystal usage, have a common ground plane. The external

components must also be connected to the ground plain. Loops must be made as small

as possible, in order to keep the noise coupled in via the PCB as small as possible. Also

parasitics should stay as small as possible. Values of C

x1

and C

x2

should be chosen

smaller accordingly to the increase in parasitics of the PCB layout.

2.3 RTC oscillator

The RTC oscillator can be used as the clock source for the RTC, and/or the watchdog

timer. Also, the RTC oscillator can be used to drive the PLL and the CPU.

3.

Register description

All registers, regardless of size, are on word address boundaries. Details of the registers

appear in the description of each function.

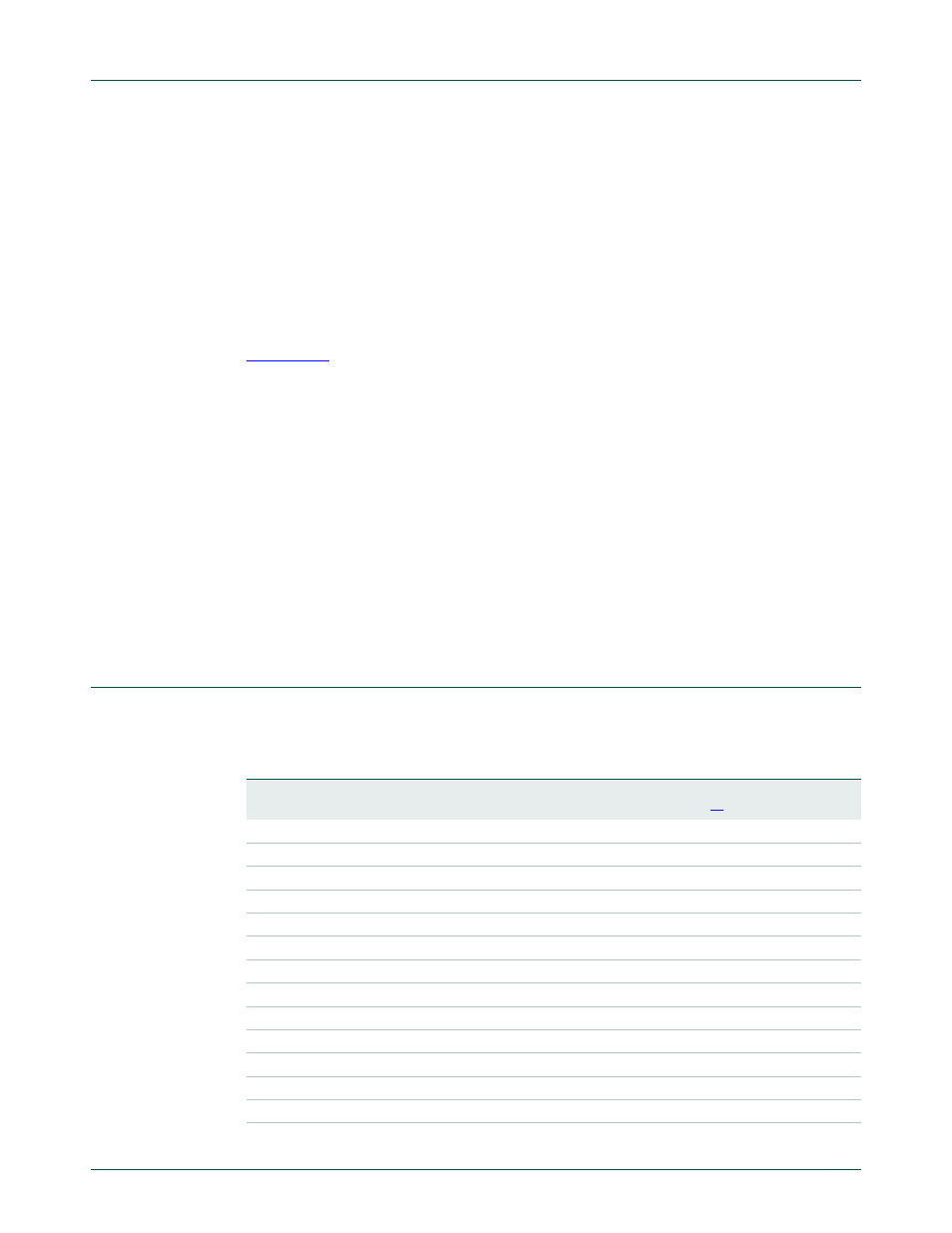

Table 41.

Summary of system control registers

Name

Description

Access

Reset

value

Address

Clock source selection

CLKSRCSEL

Clock Source Select Register

R/W

0

0xE01F C10C

Phase Locked Loop

PLLCON

PLL Control Register

R/W

0

0xE01F C080

PLLCFG

PLL Configuration Register

R/W

0

0xE01F C084

PLLSTAT

PLL Status Register

RO

0

0xE01F C088

PLLFEED

PLL Feed Register

WO

NA

0xE01F C08C

Clock dividers

CCLKCFG

CPU Clock Configuration Register

R/W

0

0xE01F C104

USBCLKCFG

USB Clock Configuration Register

R/W

0

0xE01F C108

IRCTRIM

IRC Trim Register

R/W

0xA0

0xE01F C1A4

PCLKSEL0

Peripheral Clock Selection register 0.

R/W

0

0xE01F C1A8

PCLKSEL1

Peripheral Clock Selection register 1.

R/W

0

0xE01F C1AC

Power control