Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 488

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

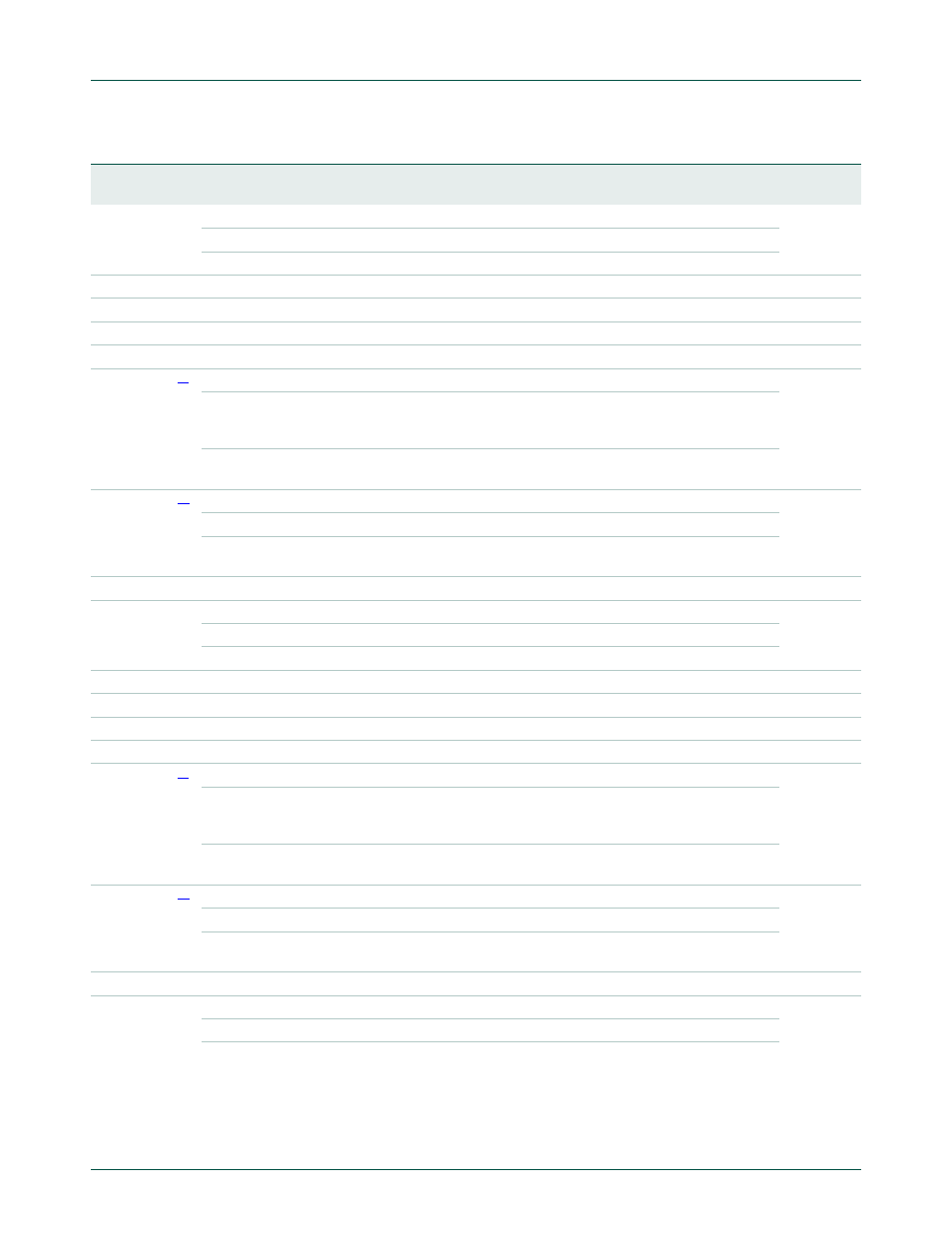

Rev. 04 — 26 August 2009

488 of 792

NXP Semiconductors

UM10237

Chapter 18: LPC24XX CAN controllers CAN1/2

5

TS1

Transmit Status 1.

1

0

0(idle)

There is no transmission from Tx Buffer 1.

1(transmit)

The CAN Controller is transmitting a message from Tx Buffer 1.

6

ES

Error Status. This bit is identical to the ES bit in the CANxGSR.

0

0

7

BS

Bus Status. This bit is identical to the BS bit in the CANxGSR.

0

0

8

RBS

Receive Buffer Status. This bit is identical to the RBS bit in the CANxGSR.

0

0

9

DOS

Data Overrun Status. This bit is identical to the DOS bit in the CANxGSR.

0

0

10

TBS2

Transmit Buffer Status 2.

1

1

0(locked)

Software cannot access the Tx Buffer 2 nor write to the corresponding

CANxTFI, CANxTID, CANxTDA, and CANxTDB registers because a

message is either waiting for transmission or is in transmitting process.

1(released)

Software may write a message into the Transmit Buffer 2 and its CANxTFI,

CANxTID, CANxTDA, and CANxTDB registers.

11

TCS2

Transmission Complete Status.

1

x

0(incomplete)

The previously requested transmission for Tx Buffer 2 is not complete.

1(complete)

The previously requested transmission for Tx Buffer 2 has been successfully

completed.

12

RS

Receive Status. This bit is identical to the RS bit in the GSR.

1

0

13

TS2

Transmit Status 2.

1

0

0(idle)

There is no transmission from Tx Buffer 2.

1(transmit)

The CAN Controller is transmitting a message from Tx Buffer 2.

14

ES

Error Status. This bit is identical to the ES bit in the CANxGSR.

0

0

15

BS

Bus Status. This bit is identical to the BS bit in the CANxGSR.

0

0

16

RBS

Receive Buffer Status. This bit is identical to the RBS bit in the CANxGSR.

0

0

17

DOS

Data Overrun Status. This bit is identical to the DOS bit in the CANxGSR.

0

0

18

TBS3

Transmit Buffer Status 3.

1

1

0(locked)

Software cannot access the Tx Buffer 3 nor write to the corresponding

CANxTFI, CANxTID, CANxTDA, and CANxTDB registers because a

message is either waiting for transmission or is in transmitting process.

1(released)

Software may write a message into the Transmit Buffer 3 and its CANxTFI,

CANxTID, CANxTDA, and CANxTDB registers.

19

TCS3

Transmission Complete Status.

1

x

0(incomplete)

The previously requested transmission for Tx Buffer 3 is not complete.

1(complete)

The previously requested transmission for Tx Buffer 3 has been successfully

completed.

20

RS

Receive Status. This bit is identical to the RS bit in the GSR.

1

0

21

TS3

Transmit Status 3.

1

0

0(idle)

There is no transmission from Tx Buffer 3.

1(transmit)

The CAN Controller is transmitting a message from Tx Buffer 3.

Table 427. Status Register (CAN1SR - address 0xE004 401C, CAN2SR - address 0xE004 801C) bit description

Bit

Symbol Value

Function

Reset

Value

RM

Set