Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 732

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

732 of 792

NXP Semiconductors

UM10237

Chapter 32: LPC24XX General Purpose DMA (GPDMA) controller

6.2.7 Lock control

Set the lock bit by programming bit 16 in the DMACCxConfiguration Register.

When a burst occurs, the AHB arbiter must not de-grant the master during the burst until

the lock is deasserted. The GPDMA can be locked for a a single burst such as a long

source fetch burst or a long destination drain burst. The GPDMA does not usually assert

the lock continuously for a source fetch burst followed by a destination drain burst.

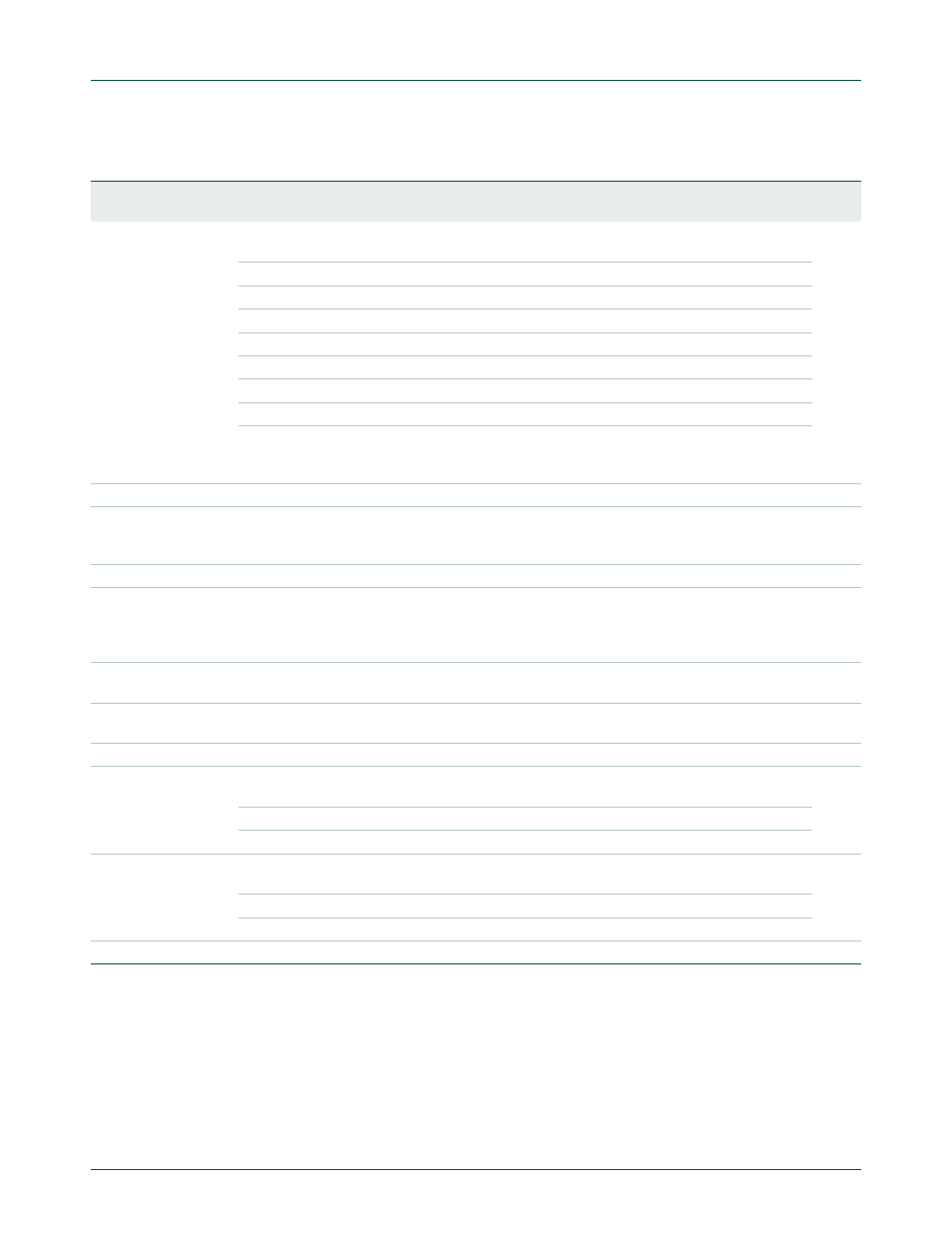

4:1

SrcPeripheral

Source peripheral. This value selects the DMA source request peripheral.This field

is ignored if the source of the transfer is from memory.

0

0000

SSP0 Tx

0001

SSP0 Rx

0010

SSP1 Tx

0011

SSP1 Rx

0100

SD/MMC

0101

I2S channel 0

0110

I2S channel 1

0111

or

1xxx

These values are reserved and should not be used.

5

-

-

Reserved, do not modify, masked on read.

NA

9:6

DestPeriphera

l

Destination peripheral. This value selects the DMA destination request peripheral.

This field is ignored if the destination of the transfer is to memory. See the

SrcPeripheral symbol description for values.

0

10

-

-

Reserved, do not modify, masked on read.

NA

13:11 FlowCntrl

Flow control and transfer type. This value indicates the flow controller and transfer

type. The flow controller can be the GPDMA, the source peripheral, or the

destination peripheral.The transfer type can be memory-to-memory,

memory-to-peripheral, peripheral-to-memory, or peripheral-to-peripheral.

0

14

IE

Interrupt error mask. When cleared this bit masks out the error interrupt of the

relevant channel.

0

15

ITC

Terminal count interrupt mask. When cleared this bit masks out the terminal count

interrupt of the relevant channel.

0

16

L

Lock. When set, this bit enables locked transfers.

0

17

A

Active. This value can be used with the Halt and Channel Enable bits to cleanly

disable a DMA channel. Writing to this bit has no effect.

0

There is no data in the FIFO of the channel.

1

The channel FIFO has data.

18

H

Halt. The contents of the channel FIFO are drained. This value can be used with the

Active and Channel Enable bits to cleanly disable a DMA channel.

0

0

Enable DMA requests.

1

Ignore further source DMA requests.

31:19 -

Reserved, do not modify, masked on read.

NA

Table 674. Channel Configuration registers (DMACC0Configuration - address 0xFFE0 4110 and

DMACC1Configuration - address 0xFFE0 4130) bit description

Bit

Symbol

Value Description

Reset

Value