4 other system controls and status flags, Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 38

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

38 of 792

NXP Semiconductors

UM10237

Chapter 3: LPC24XX System control

3.3.2.1

Examples of AHB2 settings

[1]

Sequence based on round-robin.

3.4 Other system controls and status flags

Some aspects of controlling LPC2400 operation that do not fit into peripheral or other

registers are grouped here.

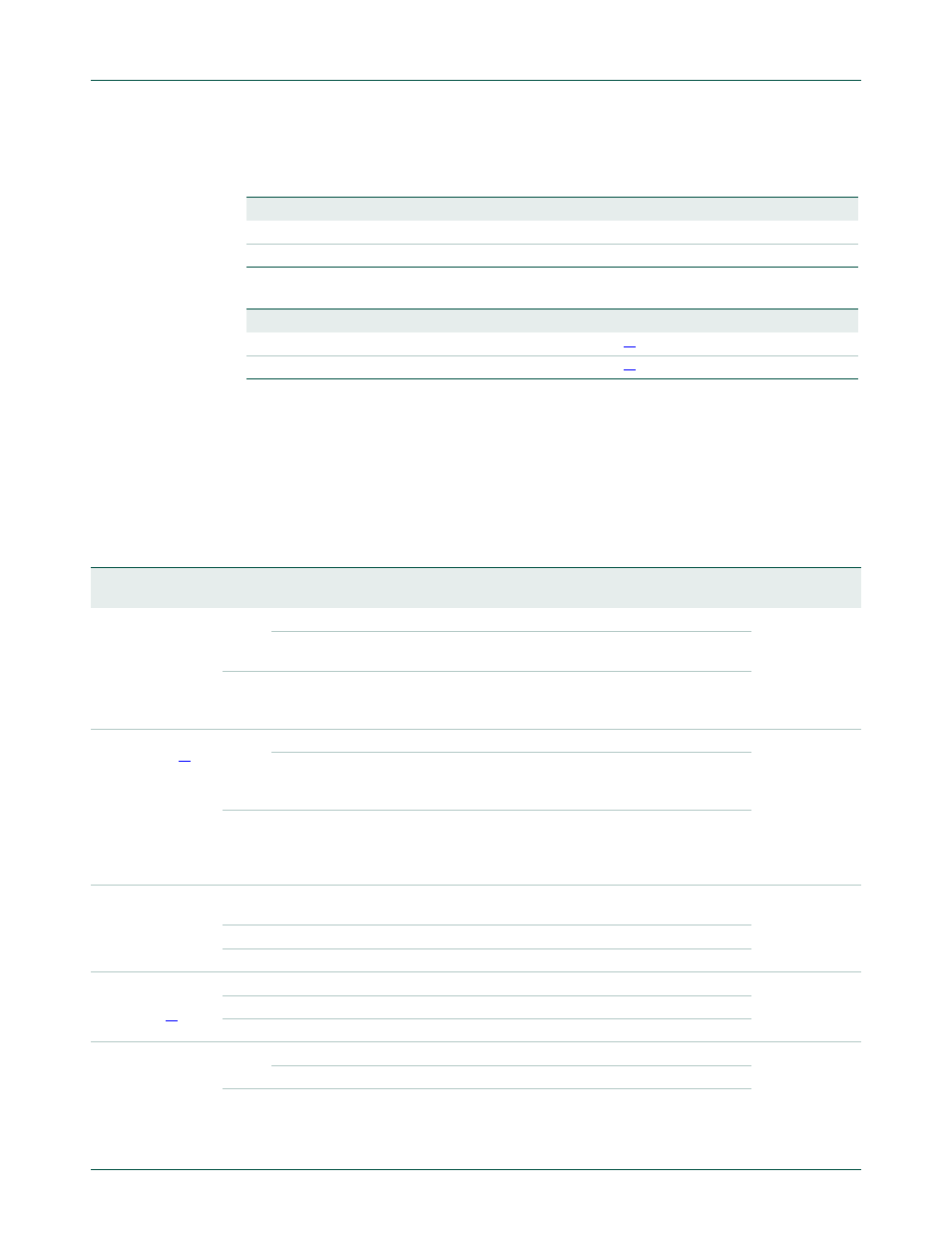

3.4.1 System Controls and Status register (SCS - 0xE01F C1A0)

Table 36.

Priority sequence (bit 0 = 0): Ethernet, CPU

Bit

Symbol

Description

Priority value nn

Priority sequence

13:12

EP1

CPU

10 (2)

1

17:16

EP2

Ethernet

01 (1)

2

Table 37.

Priority sequence (bit 0 = 0): Ethernet, CPU

Bit

Symbol

Description

Priority value nn

Priority sequence

13:12

EP1

CPU

00 2

17:16

EP2

Ethernet

00 1

Table 38.

System Controls and Status register (SCS - address 0xE01F C1A0) bit description

Bit

Symbol

Value Description

Access Reset

value

0

GPIOM

GPIO access mode selection.

R/W

0

0

GPIO ports 0 and 1 are accessed via APB addresses in a fashion

compatible with previous LPC2000 devices.

1

High speed GPIO is enabled on ports 0 and 1, accessed via addresses in

the on-chip memory range. This mode includes the port masking feature

described in the GPIO chapter.

1

EMC Reset

Disable

External Memory Controller Reset Disable.

R/W

0

0

Both EMC resets are asserted when any type of reset event occurs. In this

mode, all registers and functions of the EMC are initialized upon any reset

condition.

1

Many portions of the EMC are only reset by a power-on or brown-out event,

in order to allow the EMC to retain its state through a warm reset (external

reset or watchdog reset). If the EMC is configured correctly, auto-refresh can

be maintained through a warm reset.

2

EMC Burst

Control

External Memory Controller burst control (implemented on device revisions

C and higher).

R/W

0

0

Burst enabled.

1

Burst disabled.

3

MCIPWR

Active

Level

MCIPWR pin control.

R/W

0

0

The MCIPWR pin is low.

1

The MCIPWR pin is high.

4

OSCRANGE

Main oscillator range select.

R/W

0

0

The frequency range of the main oscillator is 1 MHz to 20 MHz.

1

The frequency range of the main oscillator is 15 MHz to 25 MHz.