Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 36

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

36 of 792

NXP Semiconductors

UM10237

Chapter 3: LPC24XX System control

3.3.1.1

Examples of AHB1 settings

The following examples use the LPC2478 to illustrate how to select the priority of each

AHB1 master based on different system requirements.

[1]

Sequence based on round-robin.

[1]

Sequence based on round-robin.

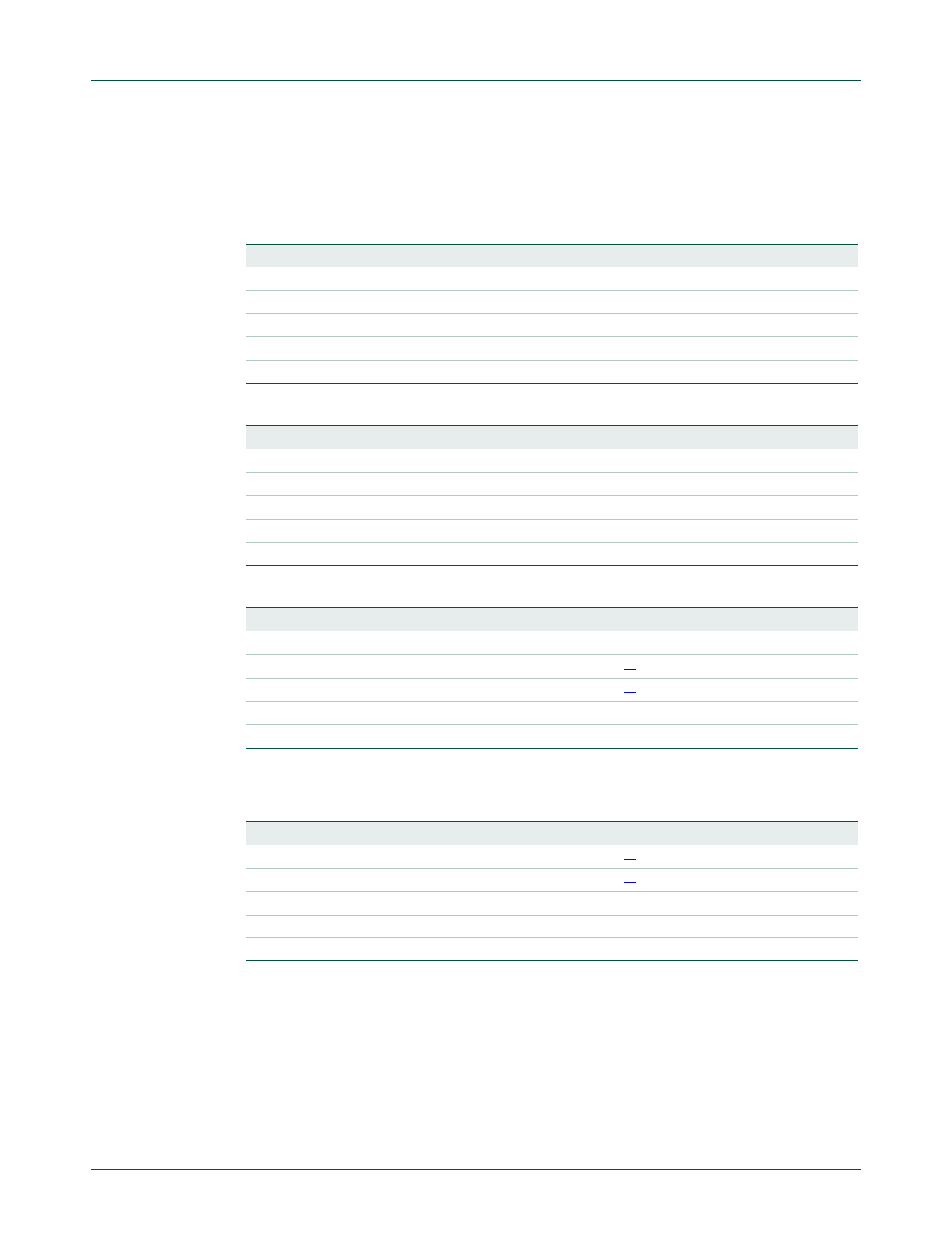

3.3.2 AHB Arbiter Configuration register 2 (AHBCFG2 - 0xE01F C18C)

By default, the AHB2 access is scheduled round-robin (bit 0 = 1). For round-robin

scheduling, the default priority sequence will be Ethernet and CPU.

The AHB2 access priority can be configured as priority scheduling (bit 0 = 0) and priority

of the each of the AHB2 bus masters can be set by writing the priority value (highest

priority = 2, lowest priority = 1).

Table 31.

Priority sequence (bit 0 = 0): LCD, CPU, GPDMA, AHB1, USB

Bit

Symbol

Description

Priority value nnn

Priority sequence

14:12

EP1

CPU

100 (4)

2

18:16

EP2

GPDMA

011 (3)

3

22:20

EP3

AHB1

010 (2)

4

26:24

EP4

USB

001 (1)

5

30:28

EP5

LCD

101 (5)

1

Table 32.

Priority sequence (bit 0 = 0): USB, AHB1, CPU, GPDMA, LCD

Bit

Symbol

Description

Priority value nnn

Priority sequence

14:12

EP1

CPU

011 (3)

3

18:16

EP2

GPDMA

010 (2)

4

22:20

EP3

AHB1

100 (4)

2

26:24

EP4

USB

101 (5)

1

30:28

EP5

LCD

001 (1)

5

Table 33.

Priority sequence (bit 0 = 0): GPDMA, AHB1, CPU, LCD, USB

Bit

Symbol

Description

Priority value nnn

Priority sequence

14:12

EP1

CPU

011 (3)

3

18:16

EP2

GPDMA

100 (4)

22:20

EP3

AHB1

100 (4)

26:24

EP4

USB

001 (1)

5

30:28

EP5

LCD

010 (2)

4

Table 34.

Priority sequence (bit 0 = 0): USB, LCD, AHB1, CPU, GPDMA

Bit

Symbol

Description

Priority value nnn

Priority sequence

14:12

EP1

CPU

000

18:16

EP2

GPDMA

000

22:20

EP3

AHB1

011 (3)

1

26:24

EP4

USB

001 (1)

3

30:28

EP5

LCD

010 (2)

2