N in, Table 11–228, Note – NXP Semiconductors LPC24XX UM10237 User Manual

Page 239: Nxp semiconductors

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

239 of 792

NXP Semiconductors

UM10237

Chapter 11: LPC24XX Ethernet

The interrupt status register is read-only. Setting can be done via the IntSet register. Reset

can be accomplished via the IntClear register.

7.4.2 Interrupt Enable Register (IntEnable - 0xFFE0 0FE4)

The Interrupt Enable register (IntEnable) has an address of 0xFFE0 0FE4. The interrupt

enable register bit definition is shown in

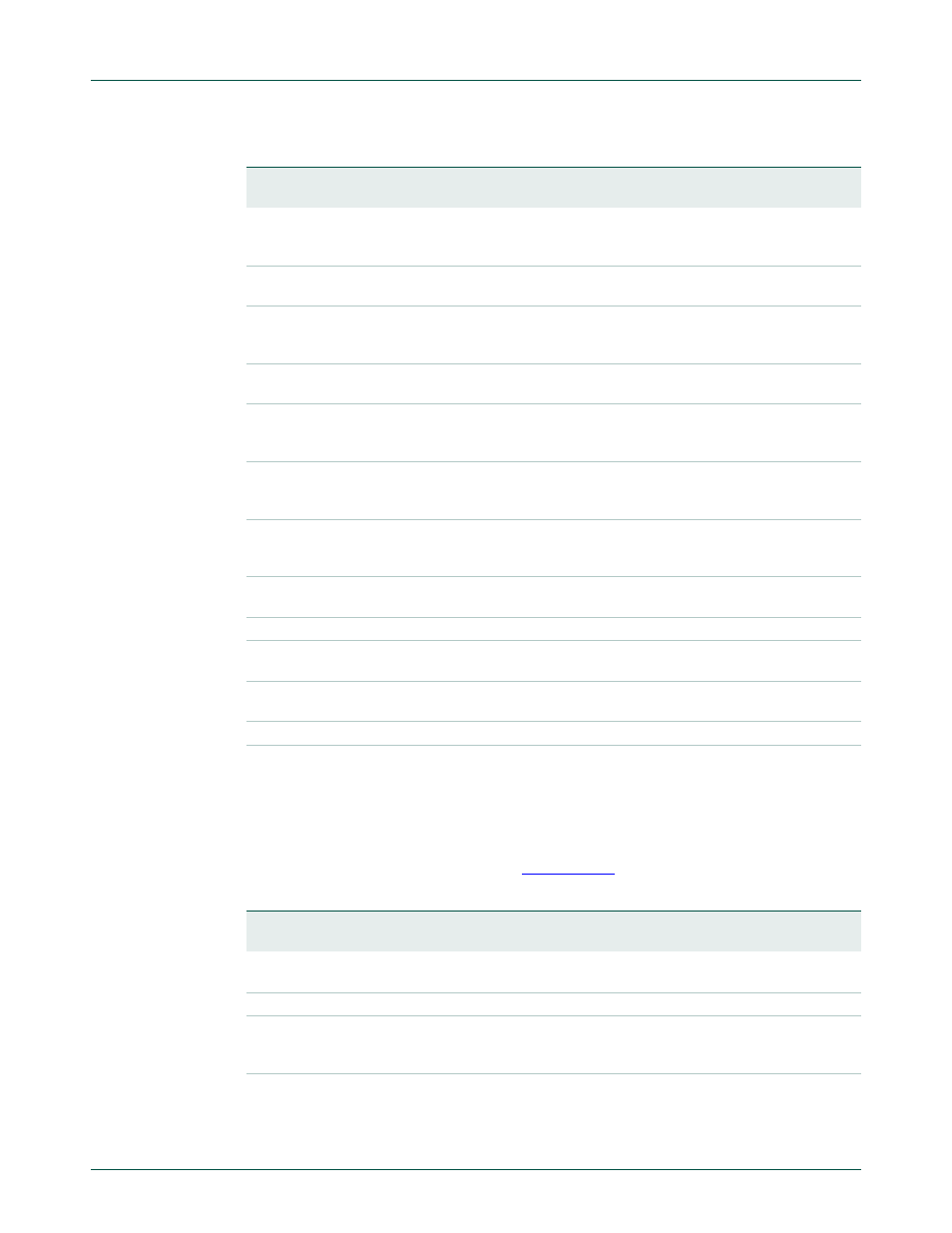

Table 228. Interrupt Status register (IntStatus - address 0xFFE0 0FE0) bit description

Bit

Symbol

Function

Reset

value

0

RxOverrunInt

Interrupt set on a fatal overrun error in the receive queue. The

fatal interrupt should be resolved by a Rx soft-reset. The bit is not

set when there is a nonfatal overrun error.

0

1

RxErrorInt

Interrupt trigger on receive errors: AlignmentError, RangeError,

LengthError, SymbolError, CRCError or NoDescriptor or Overrun.

0

2

RxFinishedInt

Interrupt triggered when all receive descriptors have been

processed i.e. on the transition to the situation where

ProduceIndex == ConsumeIndex.

0

3

RxDoneInt

Interrupt triggered when a receive descriptor has been processed

while the Interrupt bit in the Control field of the descriptor was set.

0

4

TxUnderrunInt Interrupt set on a fatal underrun error in the transmit queue. The

fatal interrupt should be resolved by a Tx soft-reset. The bit is not

set when there is a nonfatal underrun error.

0

5

TxErrorInt

Interrupt trigger on transmit errors: LateCollision,

ExcessiveCollision and ExcessiveDefer, NoDescriptor or

Underrun.

0

6

TxFinishedInt

Interrupt triggered when all transmit descriptors have been

processed i.e. on the transition to the situation where

ProduceIndex == ConsumeIndex.

0

7

TxDoneInt

Interrupt triggered when a descriptor has been transmitted while

the Interrupt bit in the Control field of the descriptor was set.

0

11:8

-

Unused

0x0

12

SoftInt

Interrupt triggered by software writing a 1 to the SoftintSet bit in

the IntSet register.

0

13

WakeupInt

Interrupt triggered by a Wakeup event detected by the receive

filter.

0

31:14

-

Unused

0x0

Table 229. Interrupt Enable register (intEnable - address 0xFFE0 0FE4) bit description

Bit

Symbol

Function

Reset

value

0

RxOverrunIntEn

Enable for interrupt trigger on receive buffer overrun or

descriptor underrun situations.

0

1

RxErrorIntEn

Enable for interrupt trigger on receive errors.

0

2

RxFinishedIntEn

Enable for interrupt triggered when all receive descriptors have

been processed i.e. on the transition to the situation where

ProduceIndex == ConsumeIndex.

0

3

RxDoneIntEn

Enable for interrupt triggered when a receive descriptor has

been processed while the Interrupt bit in the Control field of the

descriptor was set.

0