Table 32–670, Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 729

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

729 of 792

NXP Semiconductors

UM10237

Chapter 32: LPC24XX General Purpose DMA (GPDMA) controller

shows the value of the 3 bit DBSize or SBSize fields and the corresponding

burst sizes.

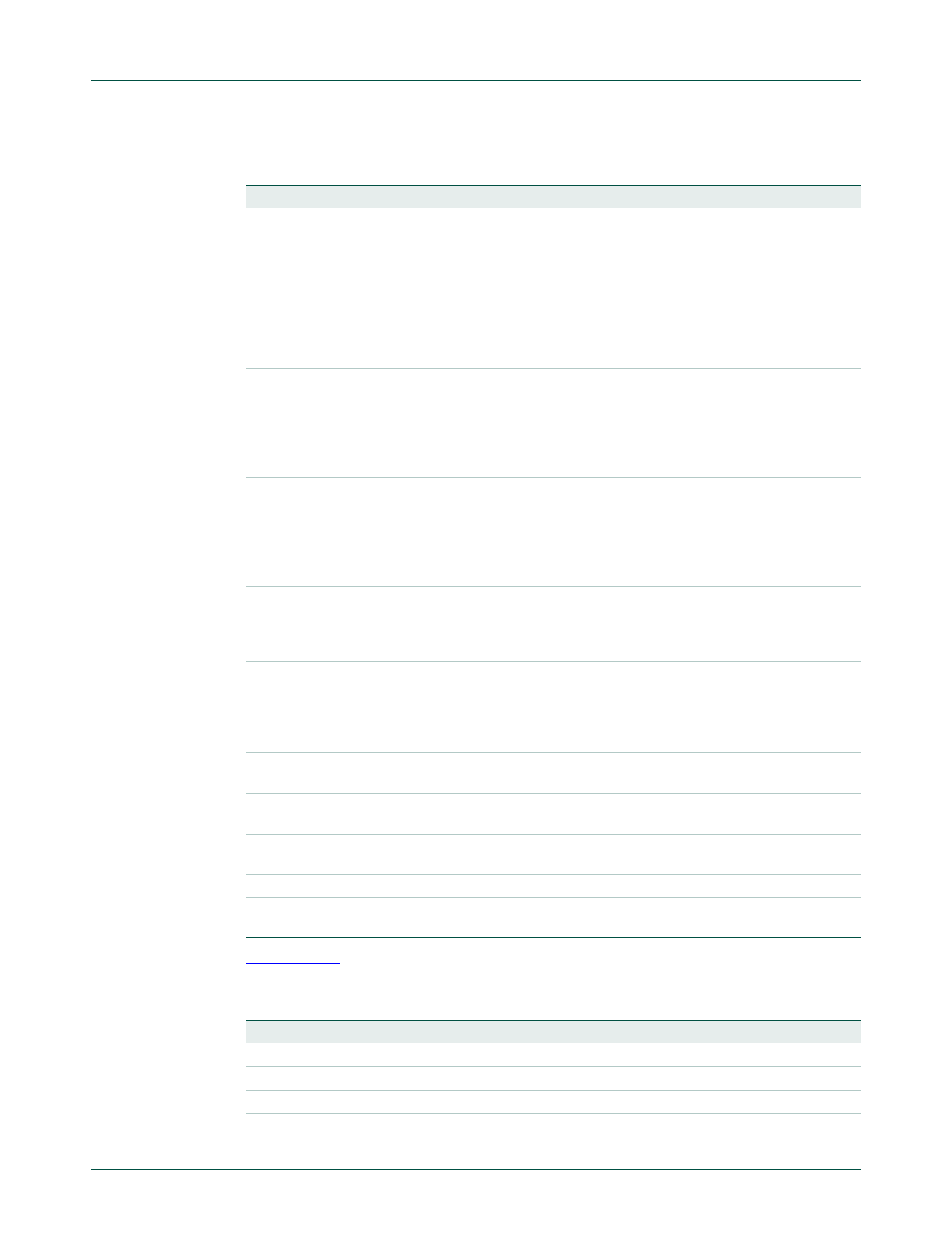

Table 670. Channel Control registers (DMACC0Control - address 0xFFE0 410C and

DMACC1Control - address 0xFFE0 412C) bit description

Bit

Symbol

Description

Reset Value

11:0

TransferSize Transfer size. A write to this field sets the size of the transfer

when the GPDMA is the flow controller.A read from this field

indicates the number of transfers completed on the

destination bus. Reading the register when the channel is

active does not give useful information because by the time

that the software has processed the value read, the channel

might have progressed. It is intended to be used only when a

channel is enabled and then disabled.The transfer size value

is not used if the GPDMA is not the flow controller.

0

14:12 SBSize

Source burst size. Indicates the number of transfers that

make up a source burst. This value must be set to the burst

size of the source peripheral, or if the source is memory, to

the memory boundary size. The burst size is the amount of

data that is transferred when the DMACBREQ signal goes

active in the source peripheral.

0

17:15 DBsize

Destination burst size. Indicates the number of transfers that

make up a destination burst transfer request. This value must

be set to the burst size of the destination peripheral, or if the

destination is memory, to the memory boundary size. The

burst size is the amount of data that is transferred when the

DMACBREQ signal goes active in the destination peripheral.

0

20:18 SWidth

Source transfer width. Transfers wider than the AHB master

bus width are illegal.The source and destination widths can

be different from each other. The hardware automatically

packs and unpacks the data as required.

0

23:21 DWidth

Destination transfer width. Transfers wider than the AHB

master bus width are not supported.The source and

destination widths can be different from each other. The

hardware automatically packs and unpacks the data as

required.

0

25:24 -

Reserved, user software should not write ones to reserved

bits. The value read from a reserved bit is not defined.

NA

26

SI

Source increment. When set the source address is

incremented after each transfer.

0

27

DI

Destination increment. When set the destination address is

incremented after each transfer.

0

30:28 Prot

Protection.

0

31

I

Terminal count interrupt enable bit. It controls whether the

current LLI is expected to trigger the terminal count interrupt.

0

Table 671. Source or destination burst size

Bit value of DBSize or SBSize

Source or distention burst transfer request size

000

1

001

4

010

8

011

16