Reset state of multiplexed pins, Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 746

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

746 of 792

NXP Semiconductors

UM10237

Chapter 34: LPC24XX Embedded Trace Module (ETM)

6.

Reset state of multiplexed pins

On the LPC2400, the ETM pin functions are multiplexed with GPIO, PWM, UART, and

CAN functions. In order to use the trace feature, the pins must be configured to select the

function. For details see

.

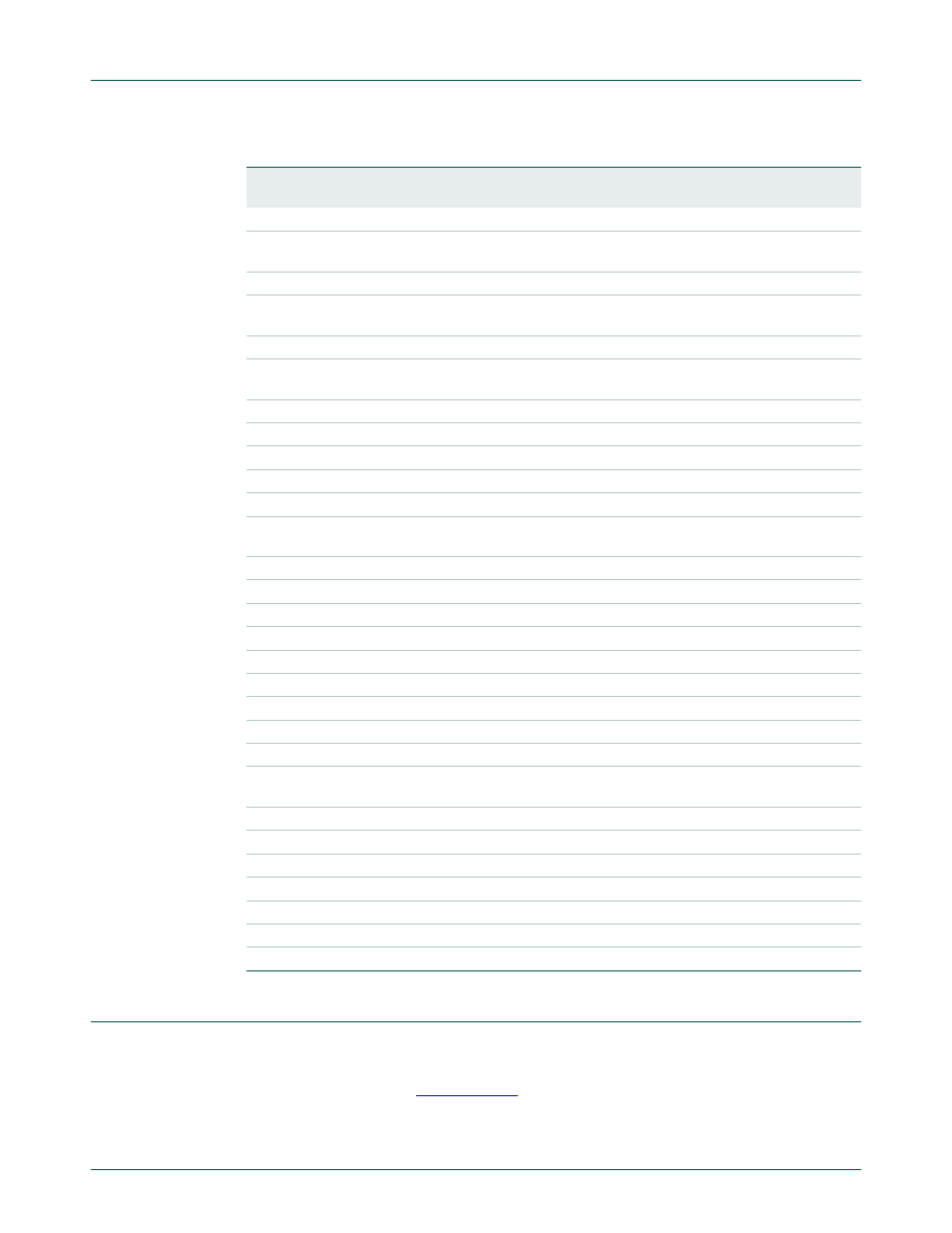

Table 681. ETM Registers

Name

Description

Access Register

Encoding

ETM Control

Controls the general operation of the ETM.

R/W

000 0000

ETM Configuration Code

Allows a debugger to read the number of

each type of resource.

RO

000 0001

Trigger Event

Holds the controlling event.

WO

000 0010

Memory Map Decode Control

Eight bit register, used to statically configure

the memory map decoder.

WO

000 0011

ETM Status

Holds the pending overflow status bit.

RO

000 0100

System Configuration

Holds the configuration information using the

SYSOPT bus.

RO

000 0101

Trace Enable Control 3

Holds the trace on/off addresses.

WO

000 0110

Trace Enable Control 2

Holds the address of the comparison.

WO

000 0111

Trace Enable Event

Holds the enabling event.

WO

000 1000

Trace Enable Control 1

Holds the include and exclude regions.

WO

000 1001

FIFOFULL Region

Holds the include and exclude regions.

WO

000 1010

FIFOFULL Level

Holds the level below which the FIFO is

considered full.

WO

000 1011

ViewData event

Holds the enabling event.

WO

000 1100

ViewData Control 1

Holds the include/exclude regions.

WO

000 1101

ViewData Control 2

Holds the include/exclude regions.

WO

000 1110

ViewData Control 3

Holds the include/exclude regions.

WO

000 1111

Address Comparator 1 to 16

Holds the address of the comparison.

WO

001 xxxx

Address Access Type 1 to 16

Holds the type of access and the size.

WO

010 xxxx

Reserved

-

-

000 xxxx

Reserved

-

-

100 xxxx

Initial Counter Value 1 to 4

Holds the initial value of the counter.

WO

101 00xx

Counter Enable 1 to 4

Holds the counter clock enable control and

event.

WO

101 01xx

Counter reload 1 to 4

Holds the counter reload event.

WO

101 10xx

Counter Value 1 to 4

Holds the current counter value.

RO

101 11xx

Sequencer State and Control

Holds the next state triggering events.

-

110 00xx

External Output 1 to 4

Holds the controlling events for each output. WO

110 10xx

Reserved

-

-

110 11xx

Reserved

-

-

111 0xxx

Reserved

-

-

111 1xxx