Table 18–425, Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 486

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

486 of 792

NXP Semiconductors

UM10237

Chapter 18: LPC24XX CAN controllers CAN1/2

Baud rate prescaler

The period of the CAN system clock t

SCL

is programmable and determines the individual

bit timing. The CAN system clock t

SCL

is calculated using the following equation:

(6)

Synchronization jump width

To compensate for phase shifts between clock oscillators of different bus controllers, any

bus controller must re-synchronize on any relevant signal edge of the current

transmission. The synchronization jump width t

SJW

defines the maximum number of clock

cycles a certain bit period may be shortened or lengthened by one re-synchronization:

(7)

Time segment 1 and time segment 2

Time segments TSEG1 and TSEG2 determine the number of clock cycles per bit period

and the location of the sample point:

(8)

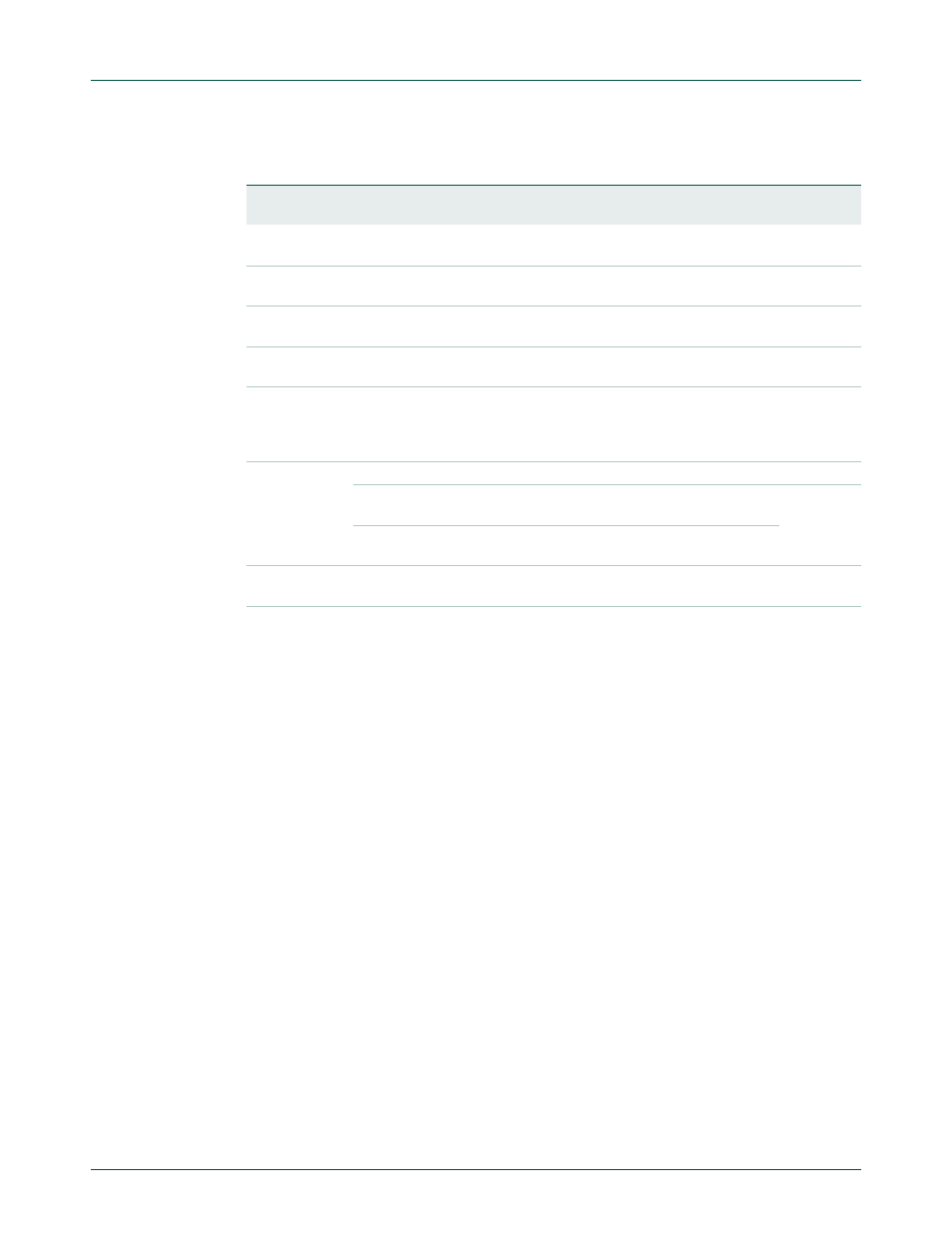

Table 425. Bus Timing Register (CAN1BTR - address 0xE004 4014, CAN2BTR - address

0xE004 8014) bit description

Bit

Symbol Value Function

Reset

Value

RM

Set

9:0

BRP

Baud Rate Prescaler. The APB clock is divided by (this

value plus one) to produce the CAN clock.

0

X

13:10 -

Reserved, user software should not write ones to reserved

bits. The value read from a reserved bit is not defined.

NA

15:14 SJW

The Synchronization Jump Width is (this value plus one)

CAN clocks.

0

X

19:16 TESG1

The delay from the nominal Sync point to the sample point

is (this value plus one) CAN clocks.

1100

X

22:20 TESG2

The delay from the sample point to the next nominal sync

point is (this value plus one) CAN clocks. The nominal CAN

bit time is (this value plus the value in TSEG1 plus 3) CAN

clocks.

001

X

23

SAM

Sampling

0

The bus is sampled once (recommended for high speed

buses)

0

X

1

The bus is sampled 3 times (recommended for low to

medium speed buses to filter spikes on the bus-line)

31:24 -

Reserved, user software should not write ones to reserved

bits. The value read from a reserved bit is not defined.

NA

t

SCL

t

CANsuppliedCLK

BRP

1

+

(

)

×

=

t

SJW

t

SCL

SJW

1

+

(

)

×

=

t

SYNCSEG

t

SCL

=