Table 17–399, Table 17–400, Table 17–401 – NXP Semiconductors LPC24XX UM10237 User Manual

Page 448: Equation 17–3, Nxp semiconductors

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

448 of 792

NXP Semiconductors

UM10237

Chapter 17: LPC24XX UART1

(3)

4.4 UART1 Interrupt Enable Register (U1IER - 0xE001 0004, when

DLAB = 0)

The U1IER is used to enable the four UART1 interrupt sources.

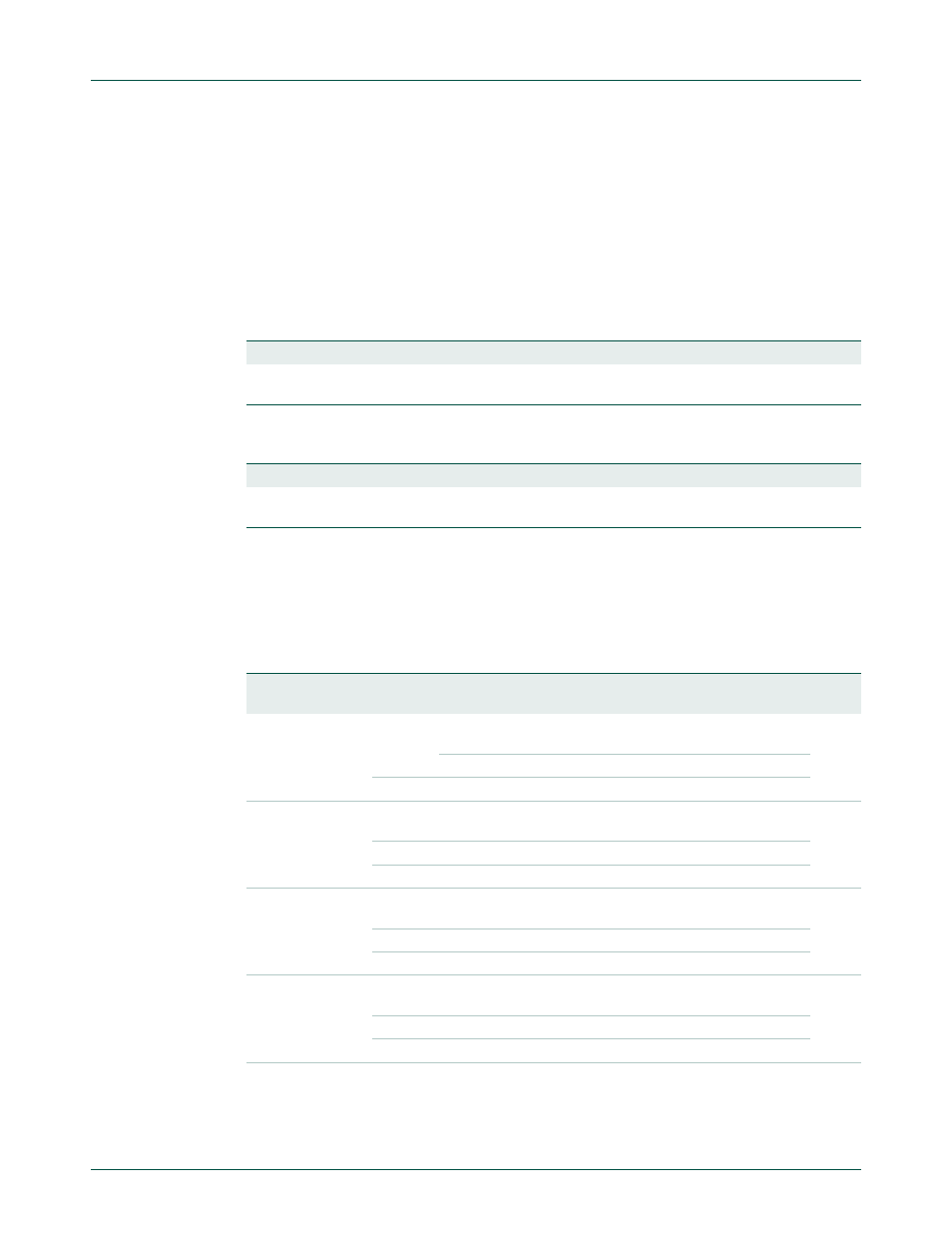

Table 399. UART1 Divisor Latch LSB Register (U1DLL - address 0xE001 0000 when

DLAB = 1) bit description

Bit

Symbol

Description

Reset Value

7:0

DLLSB

The UART1 Divisor Latch LSB Register, along with the U1DLM

register, determines the baud rate of the UART1.

0x01

Table 400. UART1 Divisor Latch MSB Register (U1DLM - address 0xE001 0004 when

DLAB = 1) bit description

Bit

Symbol

Description

Reset Value

7:0

DLMSB

The UART1 Divisor Latch MSB Register, along with the U1DLL

register, determines the baud rate of the UART1.

0x00

UART1

baudrate

pclk

16

256

U1DLM

×

U1DLL

+

(

)

×

--------------------------------------------------------------------------------

=

Table 401. UART1 Interrupt Enable Register (U1IER - address 0xE001 0004 when DLAB = 0)

bit description

Bit

Symbol

Value

Description

Reset

Value

0

RBR

Interrupt

Enable

0

enables the Receive Data Available interrupt for UART1. It

also controls the Character Receive Time-out interrupt.

0

Disable the RDA interrupts.

1

Enable the RDA interrupts.

1

THRE

Interrupt

Enable

enables the THRE interrupt for UART1. The status of this

interrupt can be read from U1LSR[5].

0

0

Disable the THRE interrupts.

1

Enable the THRE interrupts.

2

RX Line

Interrupt

Enable

enables the UART1 RX line status interrupts. The status of

this interrupt can be read from U1LSR[4:1].

0

0

Disable the RX line status interrupts.

1

Enable the RX line status interrupts.

3

Modem

Status

Interrupt

Enable

enables the modem interrupt. The status of this interrupt

can be read from U1MSR[3:0].

0

0

Disable the modem interrupt.

1

Enable the modem interrupt.

6:4

-

Reserved, user software should not write ones to reserved

bits. The value read from a reserved bit is not defined.

NA