4 module control register definitions, Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 238

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

238 of 792

NXP Semiconductors

UM10237

Chapter 11: LPC24XX Ethernet

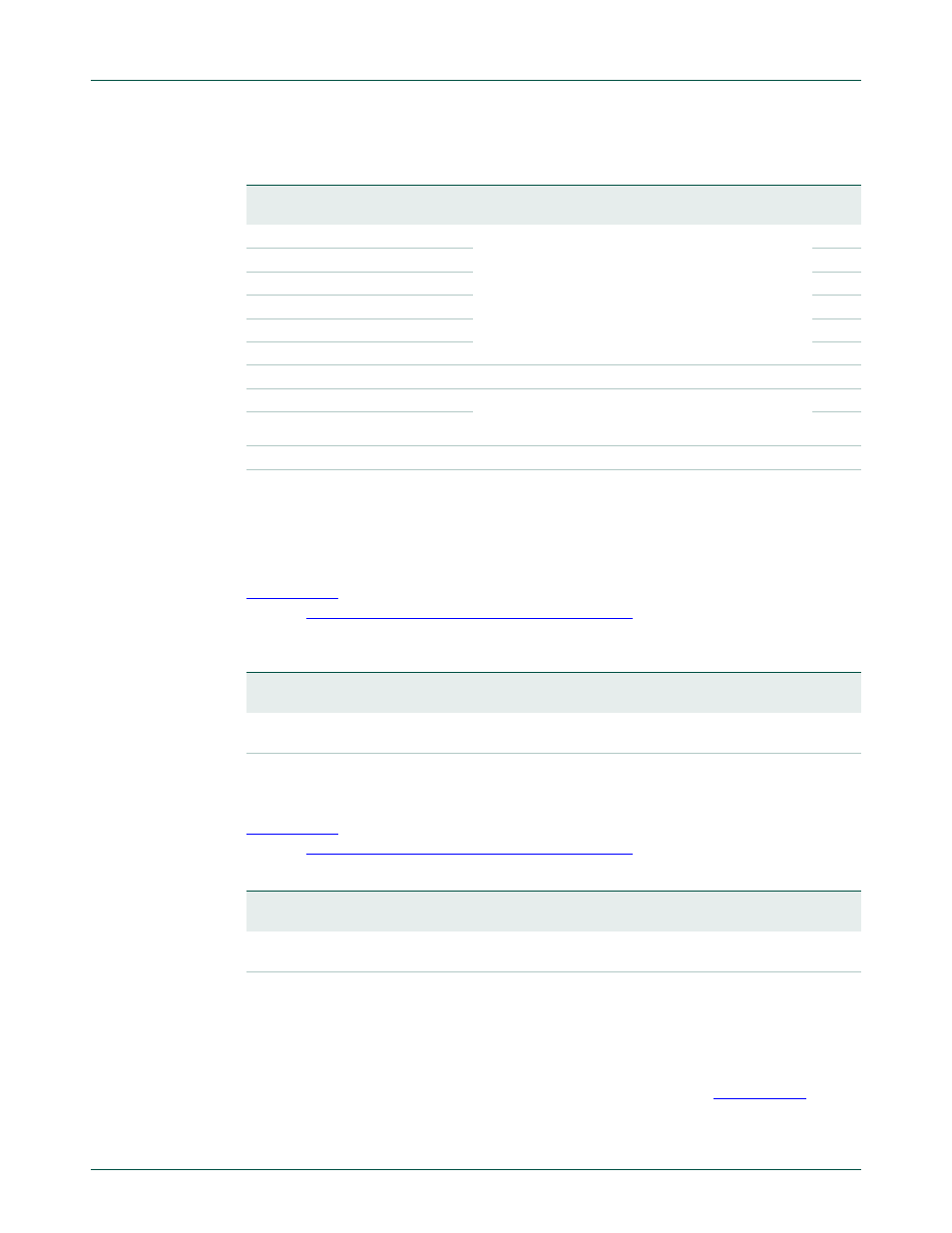

The bits in this register are write-only; writing resets the corresponding bits in the

RxFilterWoLStatus register.

7.3.4 Hash Filter Table LSBs Register (HashFilterL - 0xFFE0 0210)

The Hash Filter table LSBs register (HashFilterL) has an address of 0xFFE0 0210.

lists the bit definitions of the register. Details of Hash filter table use can be

found in

Section 11–9.13 “Receive filtering” on page 268

.

7.3.5 Hash Filter Table MSBs Register (HashFilterH - 0xFFE0 0214)

The Hash Filter table MSBs register (HashFilterH) has an address of 0xFFE0 0214.

lists the bit definitions of the register. Details of Hash filter table use can be

found in

Section 11–9.13 “Receive filtering” on page 268

.

7.4 Module control register definitions

7.4.1 Interrupt Status Register (IntStatus - 0xFFE0 0FE0)

The Interrupt Status register (IntStatus) is a Read Only register with an address of

0xFFE0 0FE0. The interrupt status register bit definition is shown in

that all bits are flip-flops with an asynchronous set in order to be able to generate

interrupts if there are wake-up events while clocks are disabled.

Table 225. Receive Filter WoL Clear register (RxFilterWoLClear - address 0xFFE0 0208) bit

description

Bit

Symbol

Function

Reset

value

0

AcceptUnicastWoLClr

When a ’1’ is written to one of these bits (0 to 5), the

corresponding status bit in the RxFilterWoLStatus

register is cleared.

0

1

AcceptBroadcastWoLClr

0

2

AcceptMulticastWoLClr

0

3

AcceptUnicastHashWoLClr

0

4

AcceptMulticastHashWoLClr

0

5

AcceptPerfectWoLClr

0

6

-

Unused

0x0

7

RxFilterWoLClr

When a ’1’ is written to one of these bits (7 and/or 8),

the corresponding status bit in the RxFilterWoLStatus

register is cleared.

0

8

MagicPacketWoLClr

0

31:9 -

Unused

0x0

Table 226. Hash Filter Table LSBs register (HashFilterL - address 0xFFE0 0210) bit

description

Bit

Symbol

Function

Reset

value

31:0

HashFilterL

Bit 31:0 of the imperfect filter hash table for receive

filtering.

0x0

Table 227. Hash Filter MSBs register (HashFilterH - address 0xFFE0 0214) bit description

Bit

Symbol

Function

Reset

value

31:0

HashFilterH

Bit 63:32 of the imperfect filter hash table for receive

filtering.

0x0