Table 5–71, Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 79

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

79 of 792

NXP Semiconductors

UM10237

Chapter 5: LPC24XX External Memory Controller (EMC)

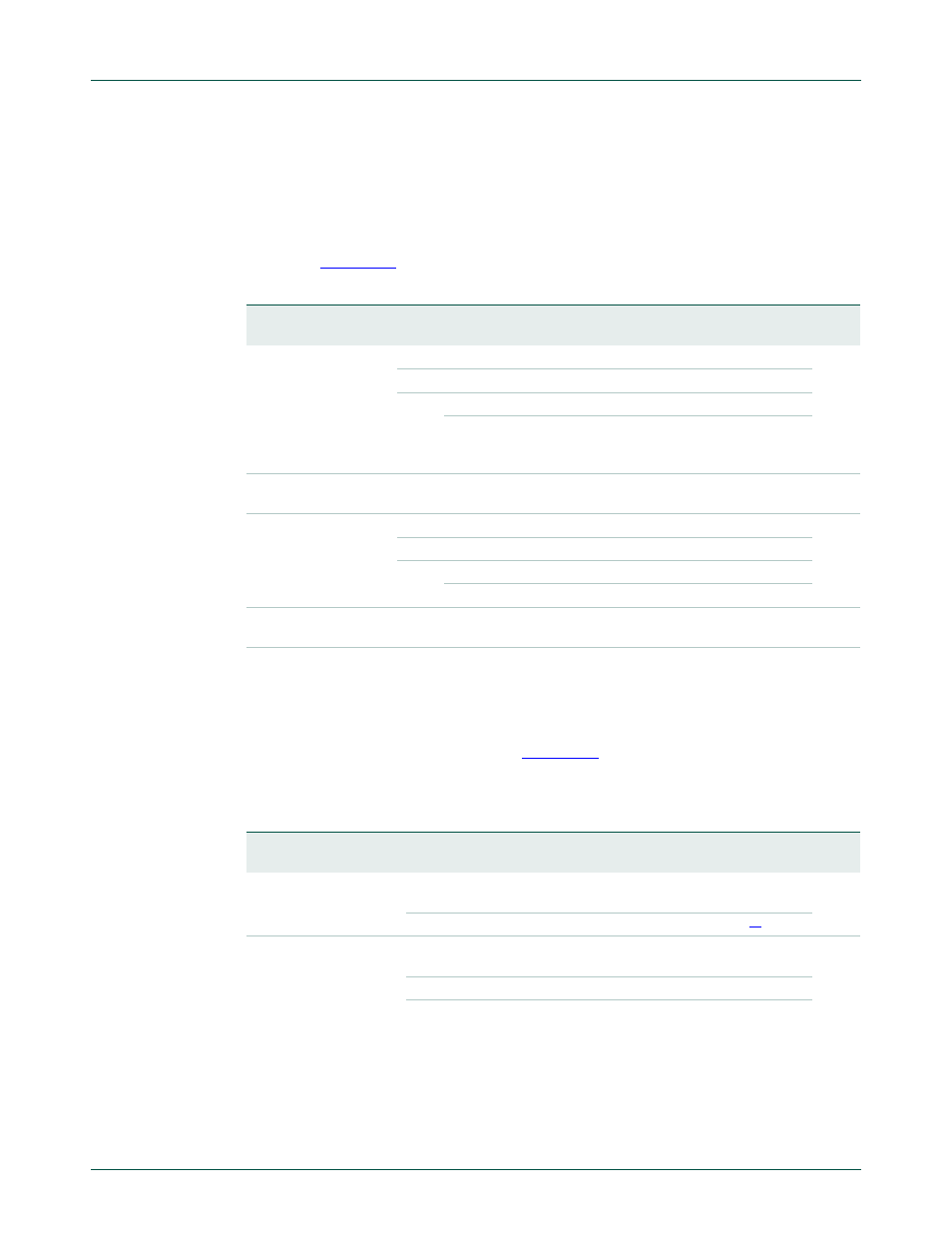

10.3 EMC Configuration register (EMCConfig - 0xFFE0 8008)

The EMCConfig register configures the operation of the memory controller. It is

recommended that this register is modified during system initialization, or when there are

no current or outstanding transactions. This can be ensured by waiting until the EMC is

idle, and then entering low-power, or disabled mode. This register is accessed with one

wait state.

shows the bit assignments for the EMCConfig register.

10.4 Dynamic Memory Control register (EMCDynamicControl -

0xFFE0 8020)

The EMCDynamicControl register controls dynamic memory operation. The control bits

can be altered during normal operation.

shows the bit assignments for the

EMCDynamicControl register.

Table 70.

EMC Configuration register (EMCConfig - address 0xFFE0 8008) bit description

Bit

Symbol

Value Description

Reset

Value

0

Endian mode:

0

0

Little-endian mode (POR reset value).

1

Big-endian mode.

On power-on reset, the value of the endian bit is 0. All

data must be flushed in the EMC before switching

between little-endian and big-endian modes.

7:1

-

-

Reserved, user software should not write ones to reserved

bits. The value read from a reserved bit is not defined.

NA

8

CCLK : CLKOUT[1:0] ratio:

0

0

1:1 (POR reset value)

1

1:2 (this option is not available on the LPC2400)

This bit must contain 0 for proper operation of the EMC.

31:9 -

-

Reserved, user software should not write ones to reserved

bits. The value read from a reserved bit is not defined.

NA

Table 71.

Dynamic Control register (EMCDynamicControl - address 0xFFE0 8020) bit

description

Bit

Symbol

Value Description

Reset

Value

0

Dynamic

memory clock

enable (CE)

0

Clock enable of idle devices are deasserted to save

power (POR reset value).

0

1

All clock enables are driven HIGH continuously.

1

Dynamic

memory clock

control (CS)

0

CLKOUT stops when all SDRAMs are idle and during

self-refresh mode.

1

1

CLKOUT runs continuously (POR reset value).

When clock control is LOW the output clock CLKOUT is

stopped when there are no SDRAM transactions. The

clock is also stopped during self-refresh mode.