3 ahb configuration, Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 34

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

34 of 792

NXP Semiconductors

UM10237

Chapter 3: LPC24XX System control

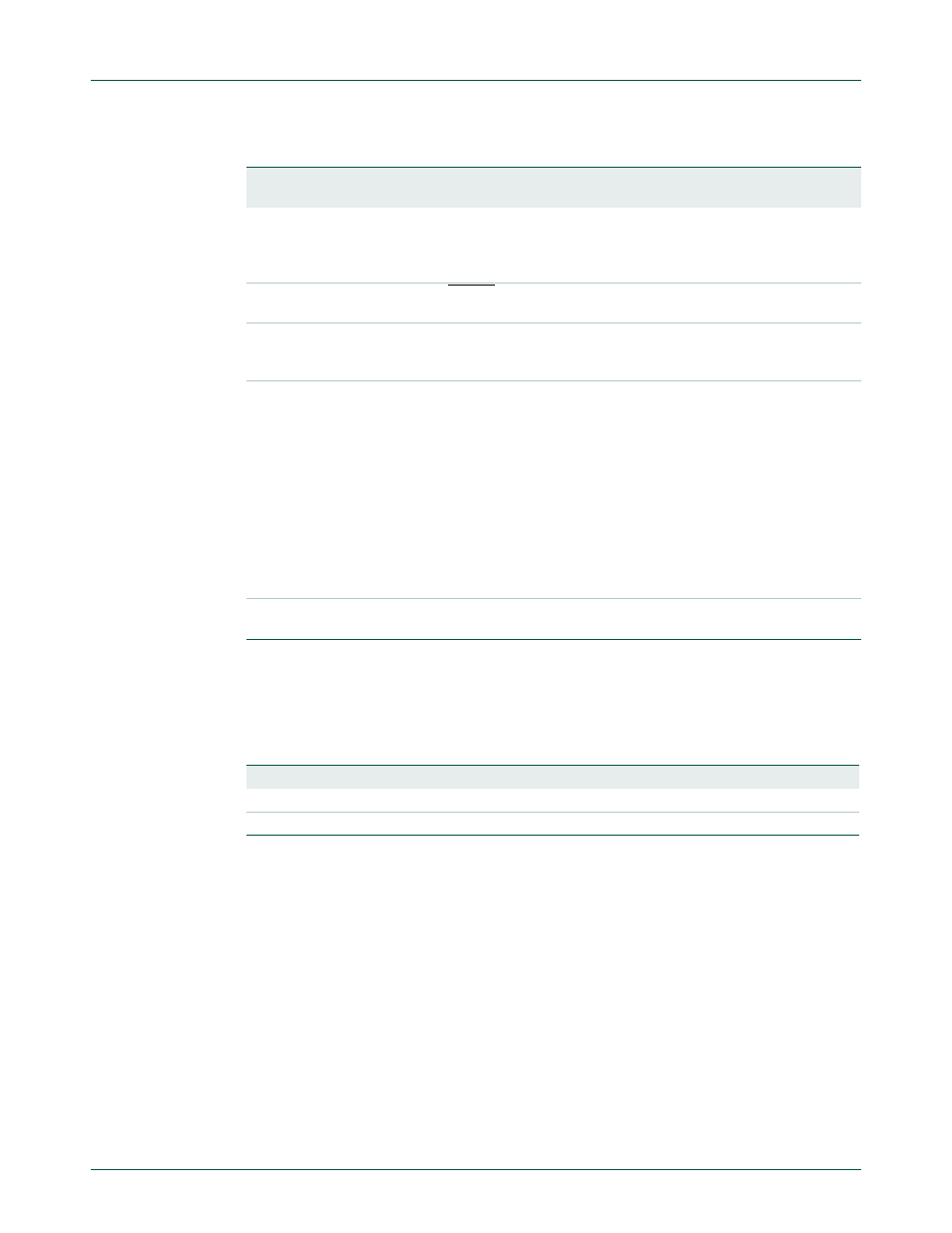

3.3 AHB Configuration

The AHB configuration register allows changing AHB scheduling and arbitration

strategies.

3.3.1 AHB Arbiter Configuration register 1 (AHBCFG1 - 0xE01F C188)

By default, the AHB1 access is scheduled round-robin (bit 0 = 1). For round-robin

scheduling, the default priority sequence will be CPU, DMA, AHB1, USB and LCD.

The AHB1 access priority can be configured as priority scheduling (bit 0 = 0) and priority

of the each of the AHB1 bus masters can be set by writing the priority value (highest

priority = 5, lowest priority = 1).

Masters with the same priority value are scheduled on a round-robin basis.

Table 28.

Reset Source Identification register (RSID - address 0xE01F C180) bit description

Bit

Symbol Description

Reset

value

0

POR

Assertion of the POR signal sets this bit, and clears all of the other bits in

this register. But if another Reset signal (e.g., External Reset) remains

asserted after the POR signal is negated, then its bit is set. This bit is not

affected by any of the other sources of Reset.

See text

1

EXTR

Assertion of the RESET signal sets this bit. This bit is cleared by POR,

but is not affected by WDT or BOD reset.

See text

2

WDTR

This bit is set when the Watchdog Timer times out and the WDTRESET

bit in the Watchdog Mode Register is 1. It is cleared by any of the other

sources of Reset.

See text

3

BODR

This bit is set when the 3.3 V power reaches a level below 2.6 V.

If the V

DD(DCDC)(3V3)

voltage dips from 3.3 V to 2.5 V and backs up, the

BODR bit will be set to 1.

If the V

DD(DCDC)(3V3)

voltage dips from 3.3 V to 2.5 V and continues to

decline to the level at which POR is asserted (nominally 1 V), the BODR

bit is cleared.

if the V

DD(DCDC)(3V3)

voltage rises continuously from below 1 V to a level

above 2.6 V, the BODR will be set to 1.

This bit is not affected by External Reset nor Watchdog Reset.

Note: Only in case when a reset occurs and the POR = 0, the BODR bit

indicates if the V

DD(DCDC)(3V3)

voltage was below 2.6 V or not.

See text

7:4

-

Reserved, user software should not write ones to reserved bits. The

value read from a reserved bit is not defined.

NA

Table 29.

AHB configuration register map

Name

Description

Access

Reset value

Address

AHBCFG1 Configures the AHB1 arbiter.

R/W

0x0000 0145

0xE01F C188

AHBCFG2 Configures the AHB2 arbiter.

R/W

0x0000 0145

0xE01F C18C