Nxp semiconductors, Fig 132. pwm block diagram – NXP Semiconductors LPC24XX UM10237 User Manual

Page 634

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

634 of 792

NXP Semiconductors

UM10237

Chapter 25: LPC24XX Pulse Width Modulator PWM0/PWM1

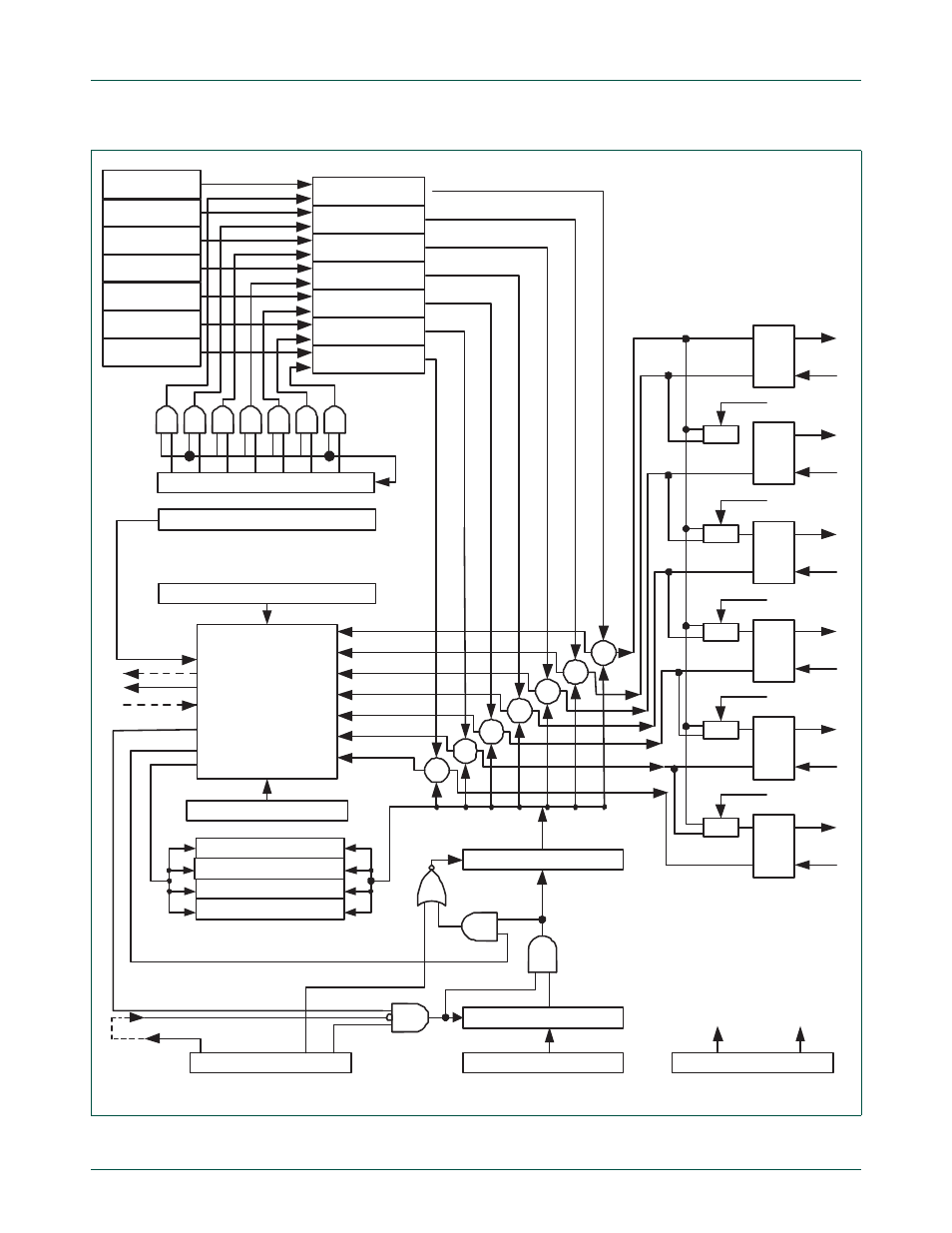

Fig 132. PWM block diagram

MATCH REGISTER 3

MATCH REGISTER 2

MATCH REGISTER 0

MATCH REGISTER 4

MATCH REGISTER 5

MATCH REGISTER 6

SHADOW REGISTER 6

LOAD ENABLE

MATCH REGISTER 1

SHADOW REGISTER 3

LOAD ENABLE

SHADOW REGISTER 2

LOAD ENABLE

SHADOW REGISTER 0

LOAD ENABLE

SHADOW REGISTER 5

LOAD ENABLE

SHADOW REGISTER 4

LOAD ENABLE

LOAD ENABLE REGISTER

CLEAR

Match0

SHADOW REGISTER 1

LOAD ENABLE

MATCH CONTROL REGISTER

INTERRUPT REGISTER

CONTROL

M[6:0]

INTERRUPT

STOP ON MATCH

RESET ON MATCH

CAPTURE[1:0]

CAPTURE CONTROL REGISTER

CAPTURE REGISTER 0

CAPTURE REGISTER 1

RESERVED

RESERVED

LOAD[1:0]

=

=

=

=

=

=

=

PWMSEL2..6

R

S

Q

EN

R

S

Q

EN

PWM6

PWMENA6

R

S

Q

EN

R

S

Q

EN

R

S

Q

EN

R

S

Q

EN

MUX

MUX

MUX

MUX

MUX

PWMSEL2

PWMSEL3

PWMSEL4

PWMSEL5

PWMSEL6

Match 0

Match 1

Match 3

Match 4

Match 5

Match 6

PWM5

PWMENA5

PWM4

PWMENA4

PWM3

PWMENA3

PWM2

PWMENA2

PWM1

PWMENA1

Match 2

TIMER CONTROL REGISTER

PRESCALE REGISTER

PWM CONTROL REGISTER

PRESCALE COUNTER

TIMER COUNTER

PWMENA1..6

MAXVAL

TCI

CE

CSN

enable

reset

master

disable