Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 156

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

156 of 792

NXP Semiconductors

UM10237

Chapter 8: LPC24XX Pin configuration

13

P0[7]/I2STX_CLK/

LCDVD[9]/SCK1/

MAT2[1]

14

P0[9]/I2STX_SDA/

LCDVD[17]/MOSI1/

MAT2[3]

15

P3[18]/D18/

PWM0[3]/CTS1

16

P4[12]/A12

17

V

DD(3V3)

-

-

-

Row D

1

TRST

2

P3[28]/D28/

CAP1[1]/PWM1[5]

3

TDO

4

P3[12]/D12

5

P3[11]/D11

6

P0[3]/RXD0

7

V

DD(3V3)

8

P3[8]/D8

9

P1[2]/ENET_TXD2/

MCICLK/PWM0[1]

10

P1[16]/ENET_MDC

11

V

DD(DCDC)(3V3)

12

V

SSCORE

13

P0[6]/I2SRX_SDA/

LCDVD[8]/SSEL1/

MAT2[0]

14

P1[7]/ENET_COL/

MCIDAT1/PWM0[5]

15

P2[2]/PWM1[3]/CTS1/

PIPESTAT1/LCDDCLK

16

P1[13]/ENET_RX_DV

17

P2[4]/PWM1[5]/

DSR1/TRACESYNC/

LCDENAB/LCDM

-

-

-

Row E

1

P0[26]/AD0[3]/

AOUT/RXD3

2

TCK

3

TMS

4

P3[3]/D3

14

P2[1]/PWM1[2]/RXD1/

PIPESTAT0/LCDLE

15

V

SSIO

16

P2[3]/PWM1[4]/DCD1/

PIPESTAT2/LCDFP

17

P2[6]/PCAP1[0]/RI1/

TRACEPKT1/

LCDVD[0]/LCDVD[4]

Row F

1

P0[25]/AD0[2]/

I2SRX_SDA/TXD3

2

P3[4]/D4

3

P3[29]/D29/

MAT1[0]/PWM1[6]

4

DBGEN

14

P4[11]/A11

15

P3[17]/D17/

PWM0[2]/RXD1

16

P2[5]/PWM1[6]/

DTR1/TRACEPKT0/

LCDLP

17

P3[16]/D16/

PWM0[1]/TXD1

Row G

1

P3[5]/D5

2

P0[24]/AD0[1]/

I2SRX_WS/CAP3[1]

3

V

DD(3V3)

4

V

DDA

14

NC

15

P4[27]/BLS1

16

P2[7]/RD2/

RTS1/TRACEPKT2/

LCDVD[1]/LCDVD[5]

17

P4[10]/A10

Row H

1

P0[23]/AD0[0]/

I2SRX_CLK/CAP3[0]

2

P3[14]/D14

3

P3[30]/D30/

MAT1[1]/RTS1

4

V

DD(DCDC)(3V3)

14

V

SSIO

15

P2[8]/TD2/TXD2/

TRACEPKT3/

LCDVD[2]/LCDVD[6]

16

P2[9]/

USB_CONNECT1/

RXD2/EXTIN0/

LCDVD[3]/LCDVD[7]

17

P4[9]/A9

Row J

1

P3[6]/D6

2

V

SSA

3

P3[31]/D31/MAT1[2]

4

NC

14

P0[16]/RXD1/

SSEL0/SSEL

15

P4[23]/A23/

RXD2/MOSI1

16

P0[15]/TXD1/

SCK0/SCK

17

P4[8]/A8

Row K

1

VREF

2

RTCX1

3

RSTOUT

4

V

SSCORE

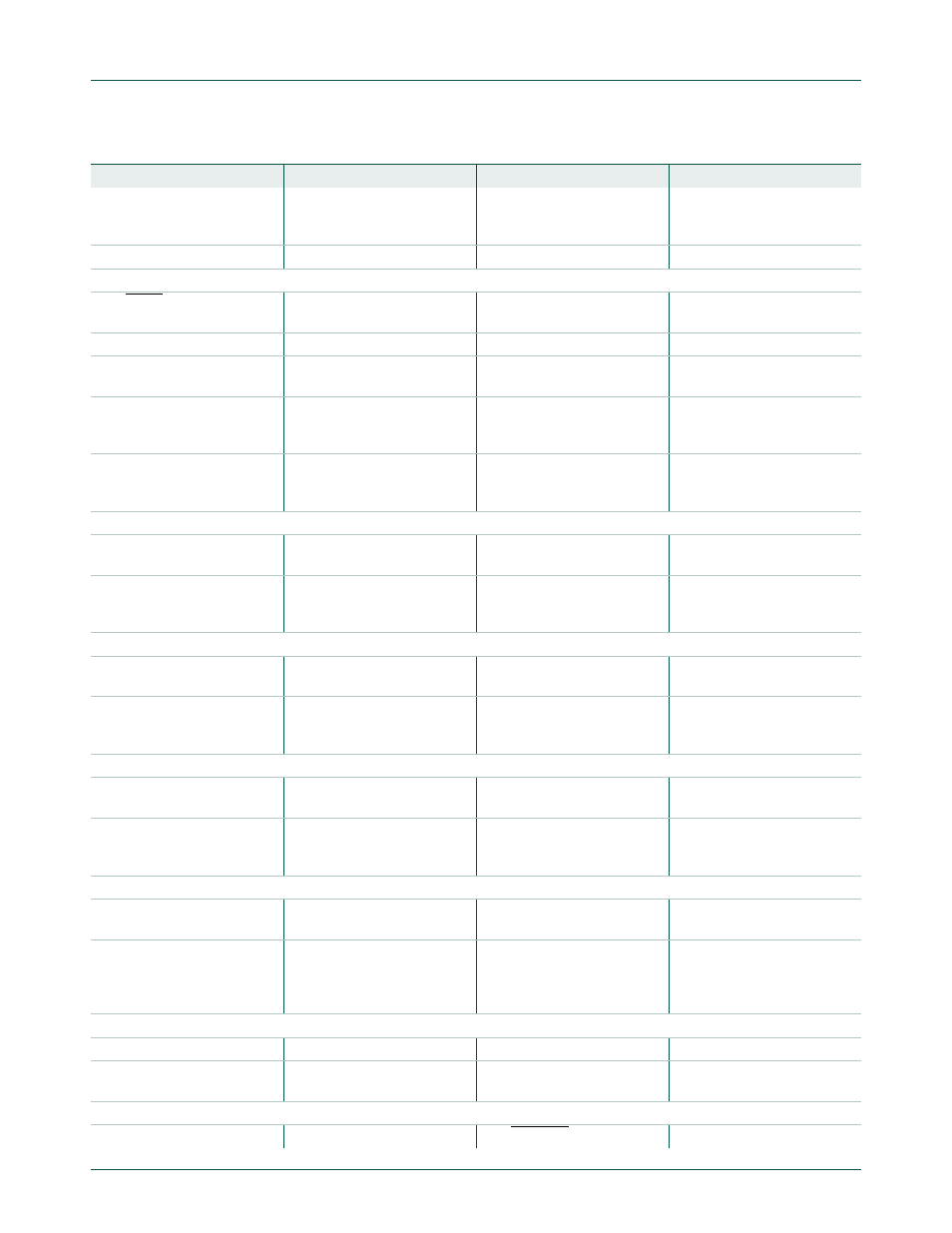

Table 123. LPC2470/78 pin allocation table

…continued

Pin Symbol

Pin Symbol

Pin Symbol

Pin Symbol