Table 10–159, Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 198

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

198 of 792

NXP Semiconductors

UM10237

Chapter 10: LPC24XX General Purpose Input/Output (GPIO)

[1]

Reset value reflects the data stored in used bits only. It does not include reserved bits content.

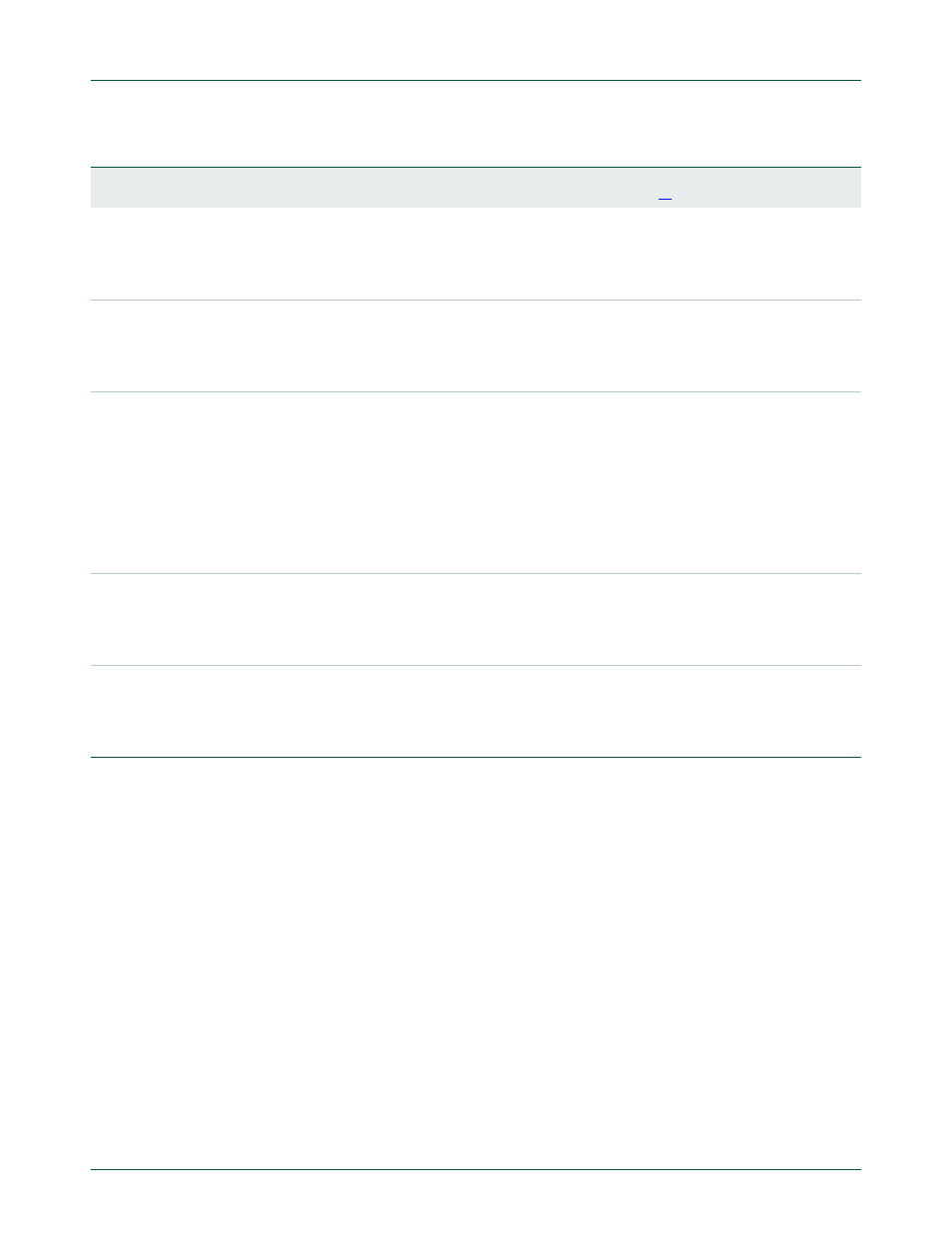

Table 159. Summary of GPIO registers (local bus accessible registers - enhanced GPIO features)

Generic

Name

Description

Access Reset

value

PORTn Register

Address & Name

FIODIR

Fast GPIO Port Direction control register. This register

individually controls the direction of each port pin.

R/W

0x0

FIO0DIR - 0x3FFF C000

FIO1DIR - 0x3FFF C020

FIO2DIR - 0x3FFF C040

FIO3DIR - 0x3FFF C060

FIO4DIR - 0x3FFF C080

FIOMASK Fast Mask register for port. Writes, sets, clears, and reads to

port (done via writes to FIOPIN, FIOSET, and FIOCLR, and

reads of FIOPIN) alter or return only the bits enabled by zeros

in this register.

R/W

0x0

FIO0MASK - 0x3FFF C010

FIO1MASK - 0x3FFF C030

FIO2MASK - 0x3FFF C050

FIO3MASK - 0x3FFF C070

FIO4MASK - 0x3FFF C090

FIOPIN

Fast Port Pin value register using FIOMASK. The current state

of digital port pins can be read from this register, regardless of

pin direction or alternate function selection (as long as pins are

not configured as an input to ADC). The value read is masked

by ANDing with inverted FIOMASK. Writing to this register

places corresponding values in all bits enabled by zeros in

FIOMASK.

Important: if a FIOPIN register is read, its bit(s) masked with 1

in the FIOMASK register will be set to 0 regardless of the

physical pin state.

R/W

0x0

FIO0PIN - 0x3FFF C014

FIO1PIN - 0x3FFF C034

FIO2PIN - 0x3FFF C054

FIO3PIN - 0x3FFF C074

FIO4PIN - 0x3FFF C094

FIOSET

Fast Port Output Set register using FIOMASK. This register

controls the state of output pins. Writing 1s produces highs at

the corresponding port pins. Writing 0s has no effect. Reading

this register returns the current contents of the port output

register. Only bits enabled by 0 in FIOMASK can be altered.

R/W

0x0

FIO0SET - 0x3FFF C018

FIO1SET - 0x3FFF C038

FIO2SET - 0x3FFF C058

FIO3SET - 0x3FFF C078

FIO4SET - 0x3FFF C098

FIOCLR

Fast Port Output Clear register using FIOMASK0. This register

controls the state of output pins. Writing 1s produces lows at

the corresponding port pins. Writing 0s has no effect. Only bits

enabled by 0 in FIOMASK0 can be altered.

WO

0x0

FIO0CLR - 0x3FFF C01C

FIO1CLR - 0x3FFF C03C

FIO2CLR - 0x3FFF C05C

FIO3CLR - 0x3FFF C07C

FIO4CLR - 0x3FFF C09C