Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 730

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

730 of 792

NXP Semiconductors

UM10237

Chapter 32: LPC24XX General Purpose DMA (GPDMA) controller

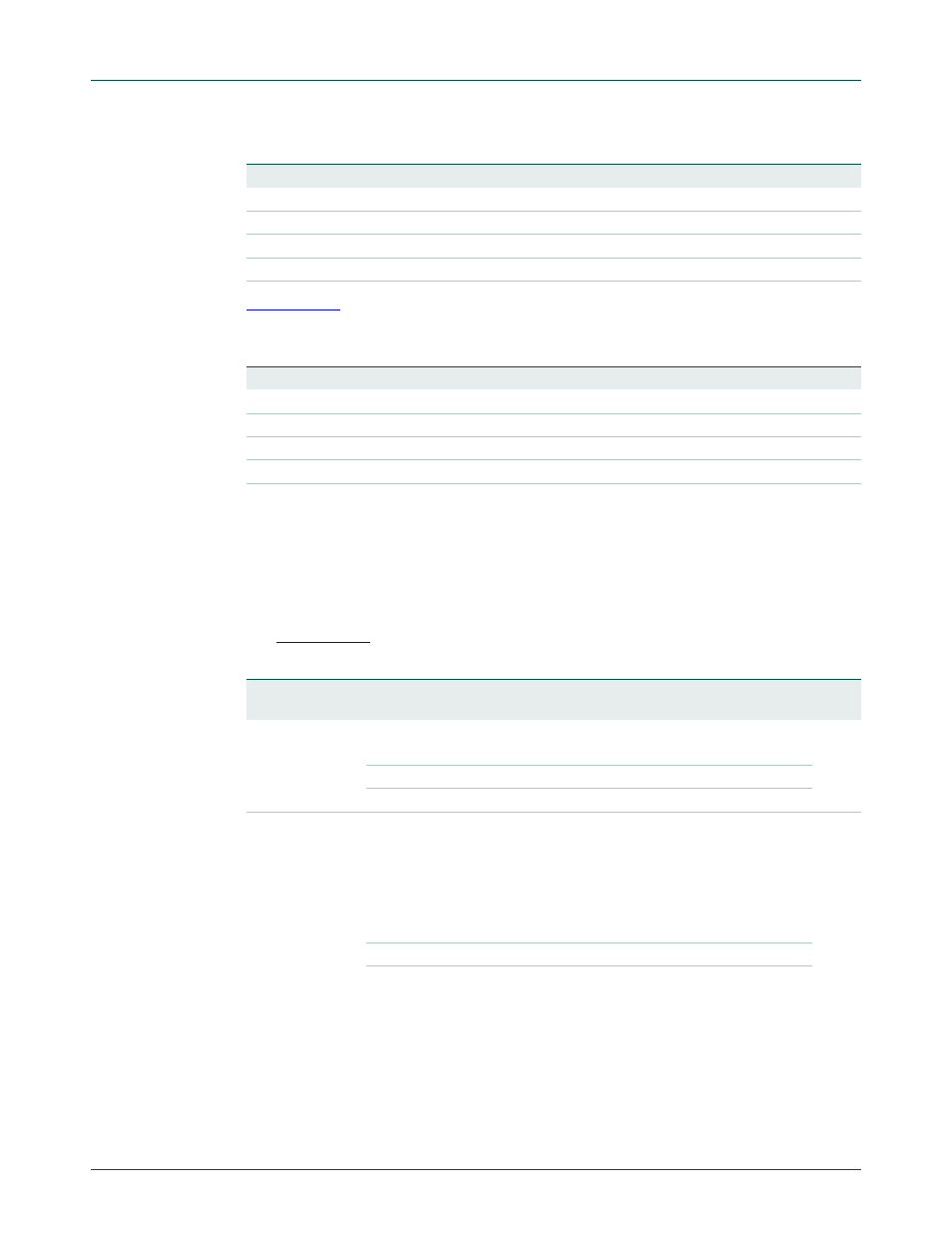

shows the value of the 3 bit SWidth or DWidth fields and the corresponding

transfer width.

6.2.5 Protection and Access Information

AHB access information is provided to the source and destination peripherals when a

transfer occurs. The transfer information is provided by programming the DMA channel

(the Prot bit of the DMACCxControl Register, and the Lock bit of the

DMACCxConfiguration Register). These bits are programmed by software and

peripherals can use this information if necessary. Three bits of information are provided,

and

shows the purpose of the three protection bits.

100

32

101

64

110

128

111

256

Table 672. Source or destination transfer width

Bit value of DBWidth or SBWidth

Source or distention burst transfer request size

000

Byte (8 bit)

001

Halfword (16 bit)

010

Word (32 bit)

011 and 1xxx

Reserved

Table 671. Source or destination burst size

Bit value of DBSize or SBSize

Source or distention burst transfer request size

Table 673. Protection bits

DMACC1Control

Bit

Value

Description

Reset

Value

28

Privileged or User. This bit controls the AHB HPROT[1] signal.

Indicates that the access is in User, or privileged mode:

0

0

User mode.

1

Privileged mode.

29

Bufferable or not bufferable. This bit indicates that the access

is bufferable. This bit can, for example, be used to indicate to

an AMBA bridge that the read can complete in zero wait states

on the source bus without waiting for it to arbitrate for the

destination bus and for the slave to accept the data. This bit

controls the AHB HPROT[2] signal.

Indicates that the access is bufferable, or not bufferable:

0

0

Not bufferable.

1

Bufferable.