Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 358

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

358 of 792

NXP Semiconductors

UM10237

Chapter 13: LPC24XX USB device controller

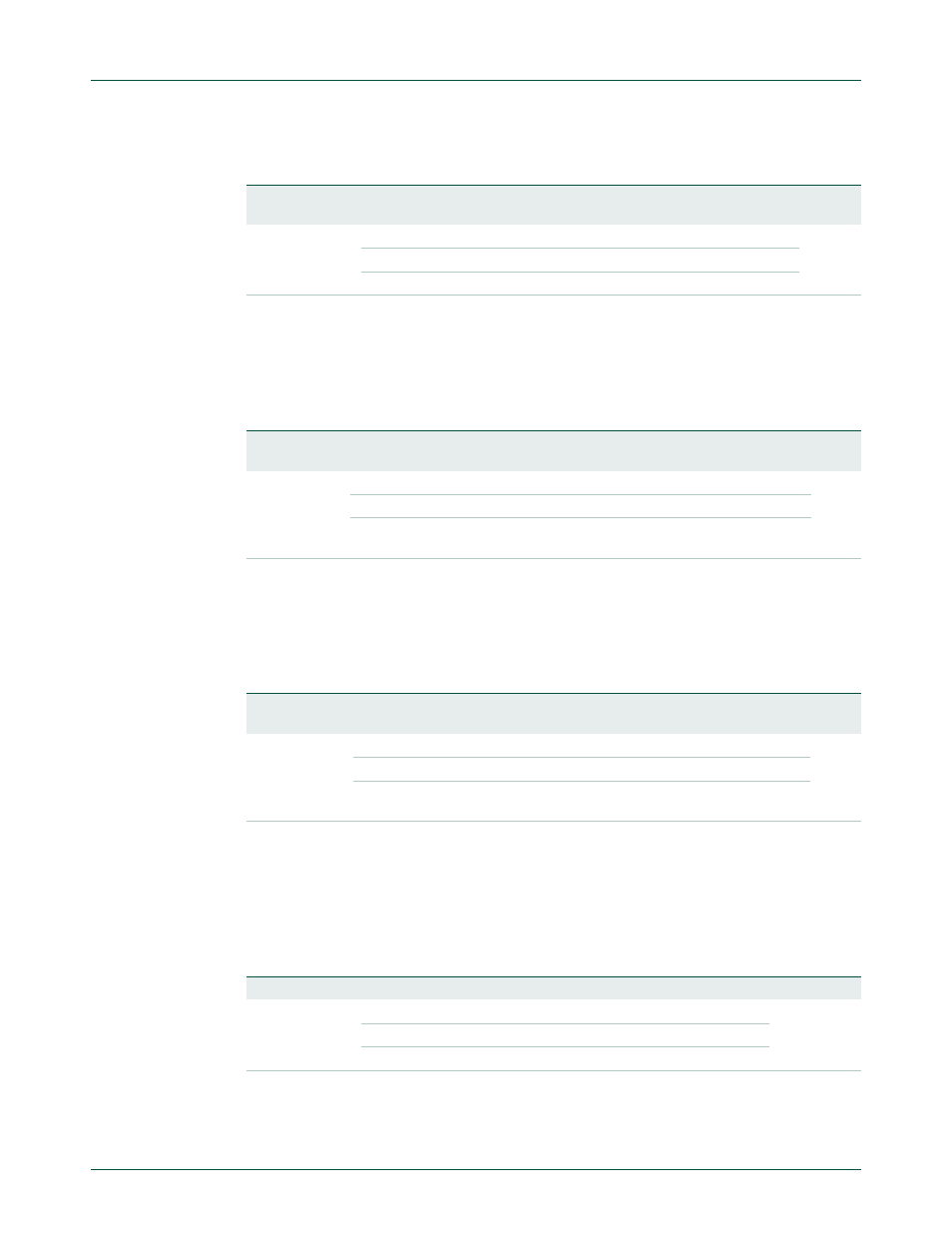

9.8.11 USB End of Transfer Interrupt Clear register (USBEoTIntClr - 0xFFE0 C2A4)

Writing one to a bit in this register clears the corresponding bit in the USBEoTIntSt

register. Writing zero has no effect. USBEoTIntClr is a write only register.

9.8.12 USB End of Transfer Interrupt Set register (USBEoTIntSet - 0xFFE0 C2A8)

Writing one to a bit in this register sets the corresponding bit in the USBEoTIntSt register.

Writing zero has no effect. USBEoTIntSet is a write only register.

9.8.13 USB New DD Request Interrupt Status register (USBNDDRIntSt - 0xFFE0

C2AC)

A bit in this register is set when a transfer is requested from the USB device and no valid

DD is detected for the corresponding endpoint. USBNDDRIntSt is a read only register.

Table 338. USB End of Transfer Interrupt Status register (USBEoTIntSt - address

0xFFE0 C2A0s) bit description

Bit

Symbol

Value

Description

Reset

value

31:0

EPxx

Endpoint xx (2

≤

xx

≤

31) End of Transfer Interrupt request.

0

0

There is no End of Transfer interrupt request for endpoint xx.

1

There is an End of Transfer Interrupt request for endpoint xx.

Table 339. USB End of Transfer Interrupt Clear register (USBEoTIntClr - address

0xFFE0 C2A4) bit description

Bit

Symbol

Value Description

Reset

value

31:0 EPxx

Clear endpoint xx (2

≤

xx

≤

31) End of Transfer Interrupt request. 0

0

No effect.

1

Clear the EPxx End of Transfer Interrupt request in the

USBEoTIntSt register.

Table 340. USB End of Transfer Interrupt Set register (USBEoTIntSet - address

0xFFE0 C2A8) bit description

Bit

Symbol

Value

Description

Reset

value

31:0

EPxx

Set endpoint xx (2

≤

xx

≤

31) End of Transfer Interrupt request.

0

0

No effect.

1

Set the EPxx End of Transfer Interrupt request in the

USBEoTIntSt register.

Table 341. USB New DD Request Interrupt Status register (USBNDDRIntSt - address

0xFFE0 C2AC) bit description

Bit

Symbol

Value

Description

Reset value

31:0

EPxx

Endpoint xx (2

≤

xx

≤

31) new DD interrupt request.

0

0

There is no new DD interrupt request for endpoint xx.

1

There is a new DD interrupt request for endpoint xx.