Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 256

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

256 of 792

NXP Semiconductors

UM10237

Chapter 11: LPC24XX Ethernet

All of the above interrupts can be enabled and disabled by setting or resetting the

corresponding bits in the IntEnable register. Enabling or disabling does not affect the

IntStatus register contents, only the propagation of the interrupt status to the CPU (via the

Vectored Interrupt Controller).

The interrupts, either of individual frames or of the whole list, are a good means of

communication between the DMA manager and the device driver, triggering the device

driver to inspect the status words of descriptors that have been processed.

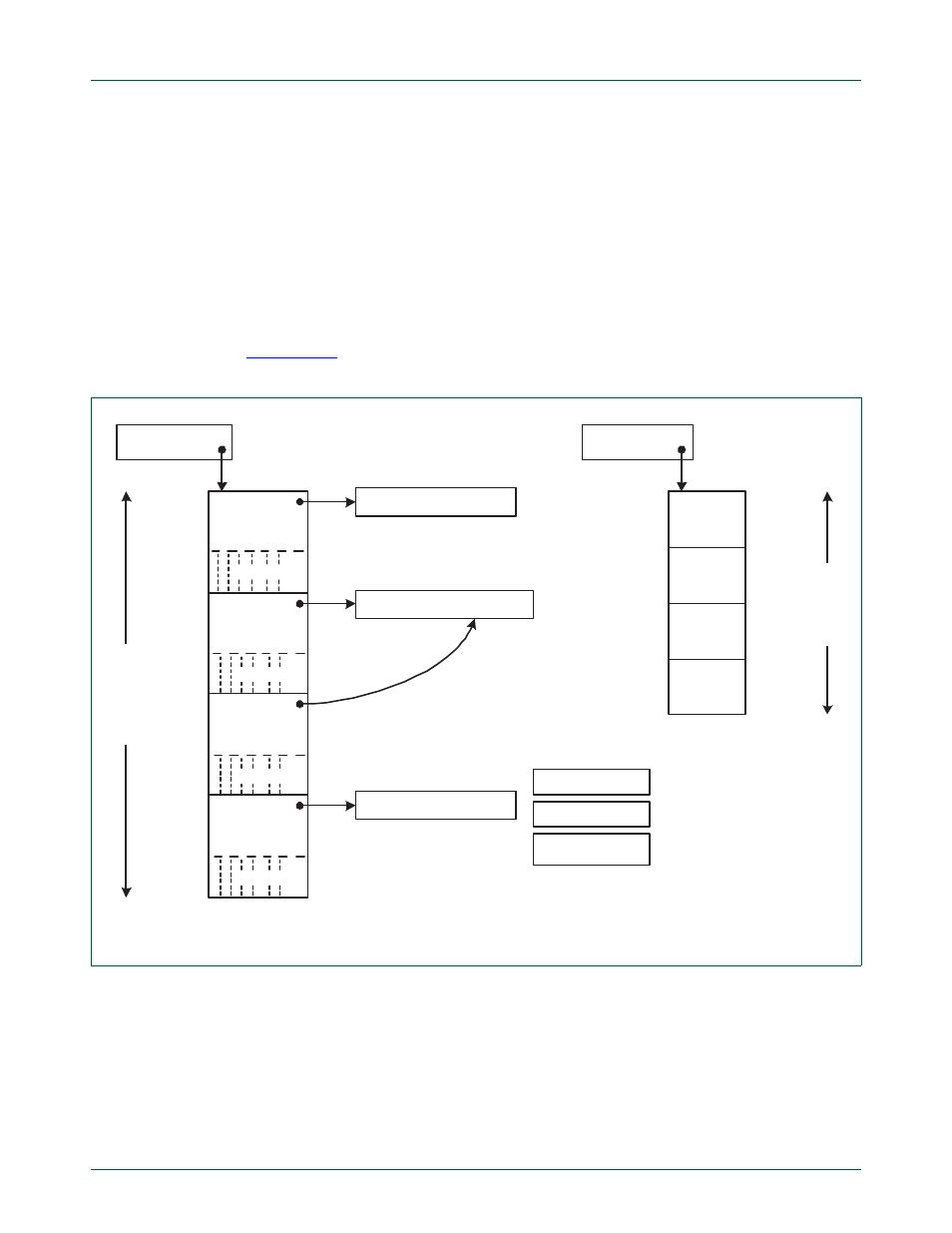

Transmit example

illustrates the transmit process in an example transmitting uses a frame

header of 8 bytes and a frame payload of 12 bytes.

After reset the values of the DMA registers will be zero. During initialization the device

driver will allocate the descriptor and status array in memory. In this example, an array of

four descriptors is allocated; the array is 4x2x4 bytes and aligned on a 4 byte address

boundary. Since the number of descriptors matches the number of statuses the status

array consists of four elements; the array is 4x1x4 bytes and aligned on a 4 byte address

boundary. The device driver writes the base address of the descriptor array

(0x7FE0 10EC) to the TxDescriptor register and the base address of the status array

Fig 30. Transmit example memory and registers

StatusInfo

StatusInfo

StatusInfo

StatusInfo

Packet

0x7FE01314

TxStatus

0x7FE011F8

TxDescriptor

0x7FE010EC

0x

7

F

E

0

1

411

0x

7F

E

0141C

0x

7

F

E

0

1

419

0

x7F

E

0

13

1

4

0x

7F

E

0

131B

0x7FE010EC

0x7FE010F0

0x7FE010F4

0x7FE010F8

0x7FE010FC

0x7FE0100

0x7FE0104

0x7FE01108

0x7FE011F8

0x7FE011FC

0x7FE01200

0x7FE01204

Packet

0x7FE01411

Packet

0x7FE01419

Packet

0x7FE01324

0x

7F

E

01324

0x

7F

E

0132

B

descriptor array

d

e

sc

ri

pt

or

0

de

s

cr

ipt

or

1

de

sc

ri

pt

or

2

d

e

sc

ri

pt

or

3

des

cr

ip

to

r ar

ra

y

fragment buffers

TxProduceIndex

TxConsumeIndex

TxDescriptorNumber

= 3

st

a

tu

s 1

sta

tu

s 0

st

a

tu

s 3

st

a

tu

s 2

st

at

us

ar

ra

y

status array

PACKET 1 HEADER (8 bytes)

PACKET 0 PAYLOAD (12 bytes)

PACKET 0 HEADER (8 bytes)

0 0

7

Control

CONTROL

0 0

7

Control

CONTROL

1 1

3

Control

CONTROL

0 0

7

Control

CONTROL