Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 308

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

308 of 792

NXP Semiconductors

UM10237

Chapter 12: LPC24XX LCD controller

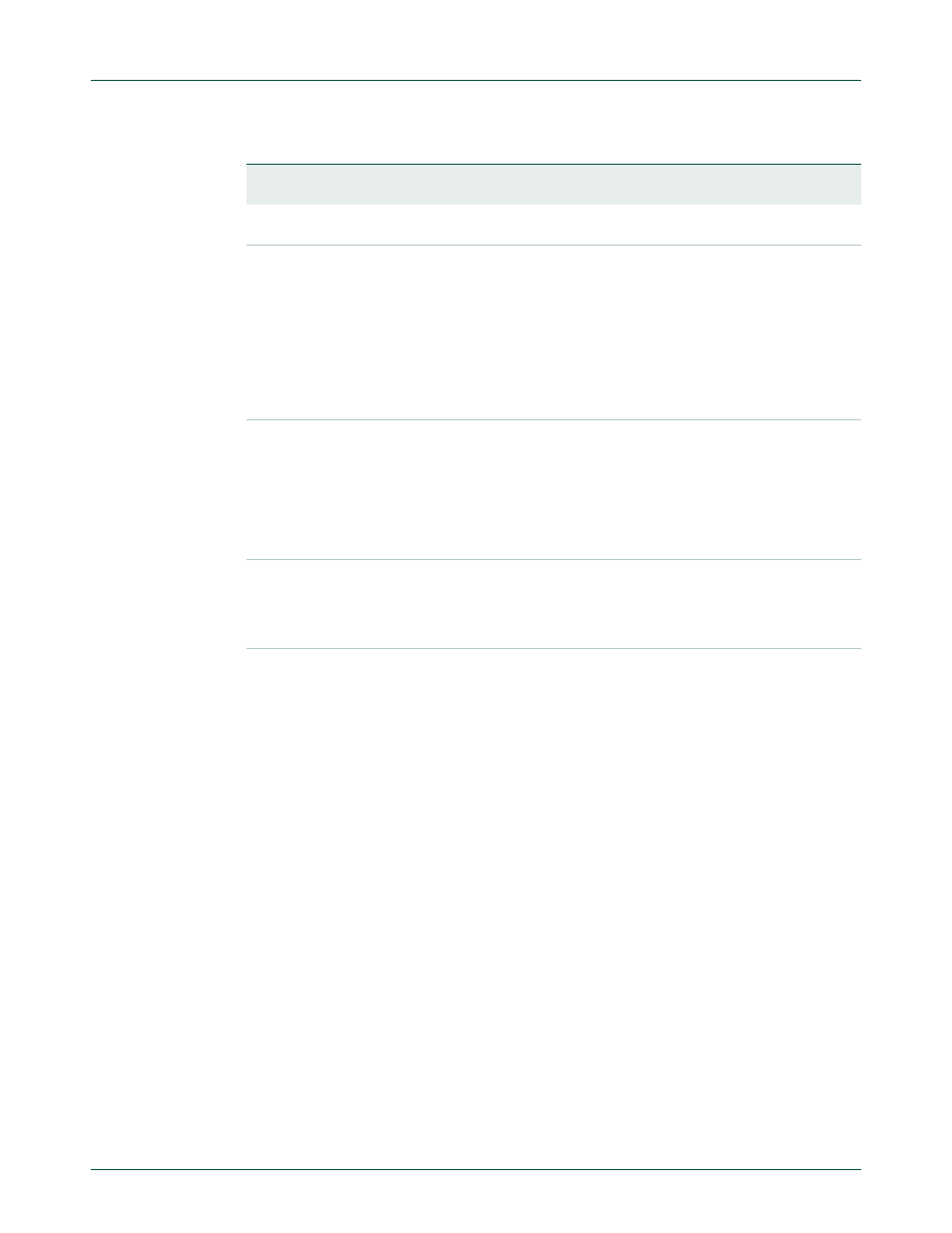

15

reserved

Reserved, user software should not write ones to reserved bits.

The value read from a reserved bit is not defined.

-

14

IOE

Invert output enable.

This bit selects the active polarity of the output enable signal in

TFT mode. In this mode, the LCDENAB pin is used as an enable

that indicates to the LCD panel when valid display data is

available. In active display mode, data is driven onto the LCD

data lines at the programmed edge of LCDDCLK when

LCDENAB is in its active state.

0 = LCDENAB output pin is active HIGH in TFT mode.

1 = LCDENAB output pin is active LOW in TFT mode.

0x0

13

IPC

Invert panel clock.

The IPC bit selects the edge of the panel clock on which pixel

data is driven out onto the LCD data lines.

0 = Data is driven on the LCD data lines on the rising edge of

LCDDCLK.

1 = Data is driven on the LCD data lines on the falling edge of

LCDDCLK.

0x0

12

IHS

Invert horizontal synchronization.

The IHS bit inverts the polarity of the LCDLP signal.

0 = LCDLP pin is active HIGH and inactive LOW.

1 = LCDLP pin is active LOW and inactive HIGH.

0x0

11

IVS

Invert vertical synchronization.

The IVS bit inverts the polarity of the LCDFP signal.

0 = LCDFP pin is active HIGH and inactive LOW.

1 = LCDFP pin is active LOW and inactive HIGH.

0x0

Table 263. Clock and Signal Polarity register (LCD_POL, RW - 0xFFE1 0008)

Bits

Function

Description

Reset

value