2 example phy devices, 3 dma engine functions, Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 215

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

215 of 792

NXP Semiconductors

UM10237

Chapter 11: LPC24XX Ethernet

A receive filter block is used to identify received frames that are not addressed to this

Ethernet station, so that they can be discarded. The Rx filters include a perfect address

filter and a hash filter.

Wake-on-LAN power management support makes it possible to wake the system up from

a power-down state -a state in which some of the clocks are switched off -when wake-up

frames are received over the LAN. Wake-up frames are recognized by the receive filtering

modules or by a Magic Frame detection technology. System wake-up occurs by triggering

an interrupt.

An interrupt logic block raises and masks interrupts and keeps track of the cause of

interrupts. The interrupt block sends an interrupt request signal to the host system.

Interrupts can be enabled, cleared and set by software.

Support for IEEE 802.3/clause 31 flow control is implemented in the flow control block.

Receive flow control frames are automatically handled by the MAC. Transmit flow control

frames can be initiated by software. In half duplex mode, the flow control module will

generate back pressure by sending out continuous preamble only, interrupted by pauses

to prevent the jabber limit from being exceeded.

The Ethernet block has both a standard IEEE 802.3/clause 22 Media Independent

Interface (MII) bus and a Reduced Media Independent Interface (RMII) to connect to an

external Ethernet PHY chip. MII or RMII mode can be selected by the RMII bit in the

Command register. The standard nibble-wide MII interface allows a low speed data

connection to the PHY chip: 2.5 MHz at 10 Mbps or 25 MHz at 100 Mbps. The RMII

interface allows a low pin count double clock data connection to the PHY. Registers in the

PHY chip are accessed via the AHB interface through the serial management connection

of the MII bus (MIIM) operating at 2.5 MHz.

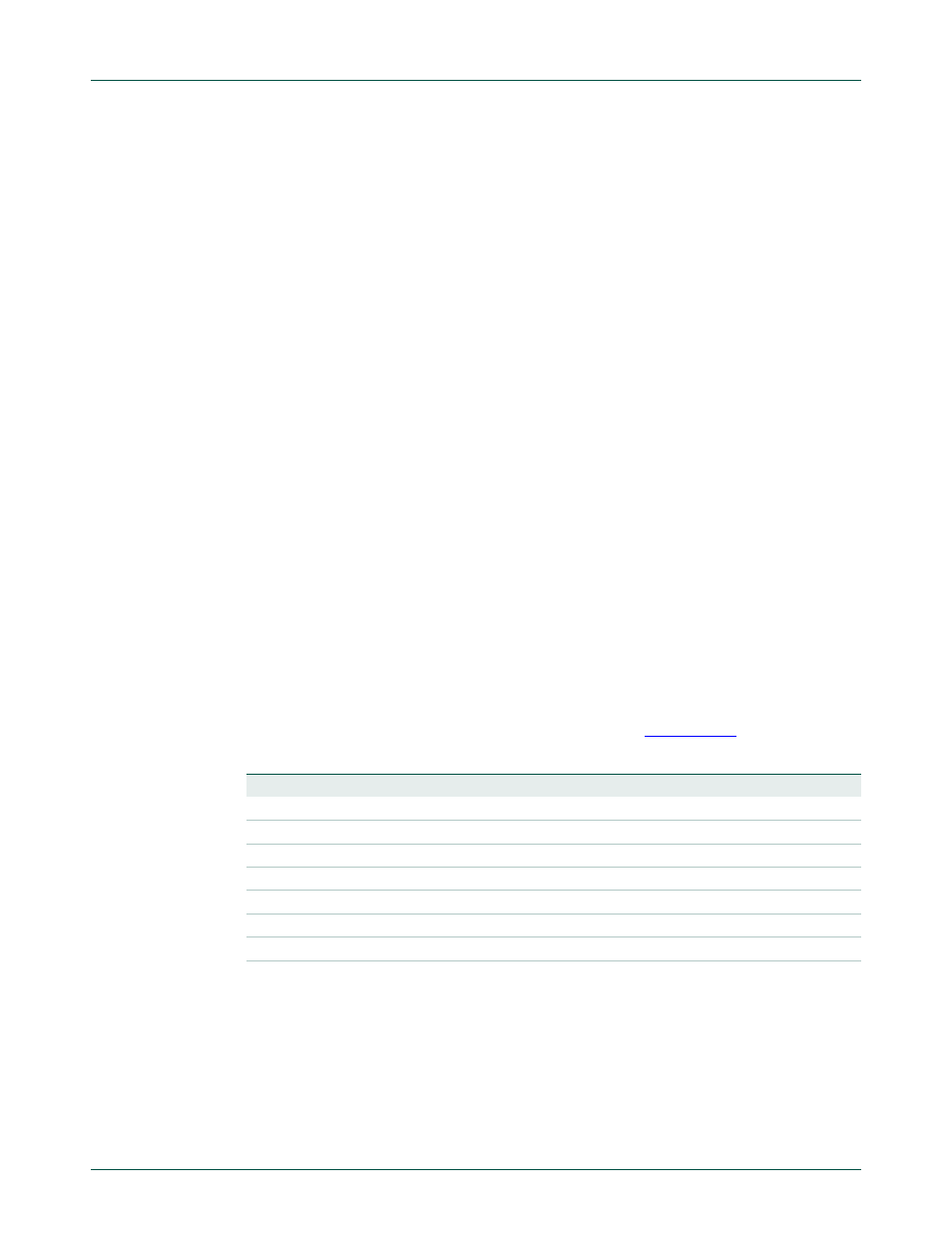

5.2 Example PHY Devices

Some examples of compatible PHY devices are shown in

.

5.3 DMA engine functions

The Ethernet block is designed to provide optimized performance via DMA hardware

acceleration. Independent scatter/gather DMA engines connected to the AHB bus off-load

many data transfers from the ARM7 CPU.

Table 182. Example PHY Devices

Manufacturer

Part Number(s)

Broadcom

BCM5221

ICS

ICS1893

Intel

LXT971A

LSI Logic

L80223, L80225, L80227

Micrel

KS8721

National

DP83847, DP83846, DP83843

SMSC

LAN83C185