6 alarm output, 7 rtc clock generation, Section 26–6.6 “alarm output – NXP Semiconductors LPC24XX UM10237 User Manual

Page 656: Section 26–6.7, Section 26–6.6, Section 26–6.7.1, Table 26–578, Nxp semiconductors

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

656 of 792

NXP Semiconductors

UM10237

Chapter 26: LPC24XX Real-Time Clock (RTC) and battery RAM

6.6 Alarm output

The RTC includes an alarm output pin that reflects both the alarm comparisons and

interrupts from the RTC. This pin is in the RTC power domain, and therefore it is available

during all power saving modes as long as power is supplied to VBAT. Since the alarm pin

combines the alarm and interrupt functions of the RTC, either a specific time/date/etc. or a

periodic interval can be provided to the outside world. For example, a time-of-day alarm

could be used to tell external circuitry to turn on power to the LPC2400 in order to wake up

from Deep power-down mode.

6.7 RTC clock generation

The RTC may be clocked by either the 32.786 kHz RTC oscillator, or by the APB

peripheral clock (PCLK) after adjustment by the reference clock divider.

6.7.1 Reference Clock Divider (Prescaler)

The reference clock divider (hereafter referred to as the Prescaler) may be used when the

RTC clock source is not supplied by the RTC oscillator, but comes from the APB

peripheral clock (PCLK).

The Prescaler allows generation of a 32.768 kHz reference clock from any PCLK

frequency greater than or equal to 65.536 kHz (2

× 32.768 kHz). This permits the RTC to

always run at the proper rate regardless of the peripheral clock rate. Basically, the

Prescaler divides PCLK by a value which contains both an integer portion and a fractional

portion. The result is not a continuous output at a constant frequency, some clock periods

will be one PCLK longer than others. However, the overall result can always be 32,768

counts per second.

The reference clock divider consists of a 13 bit integer counter and a 15 bit fractional

counter. The reasons for these counter sizes are as follows:

1. For frequencies that are expected to be supported by the LPC2400, a 13 bit integer

counter is required. This can be calculated as 160 MHz divided by 32,768 minus 1

equals 4881 with a remainder of 26,624. Thirteen bits are needed to hold the value

4881, but actually supports frequencies up to 268.4 MHz (32,768

× 8192).

2. The remainder value could be as large as 32,767, which requires 15 bits.

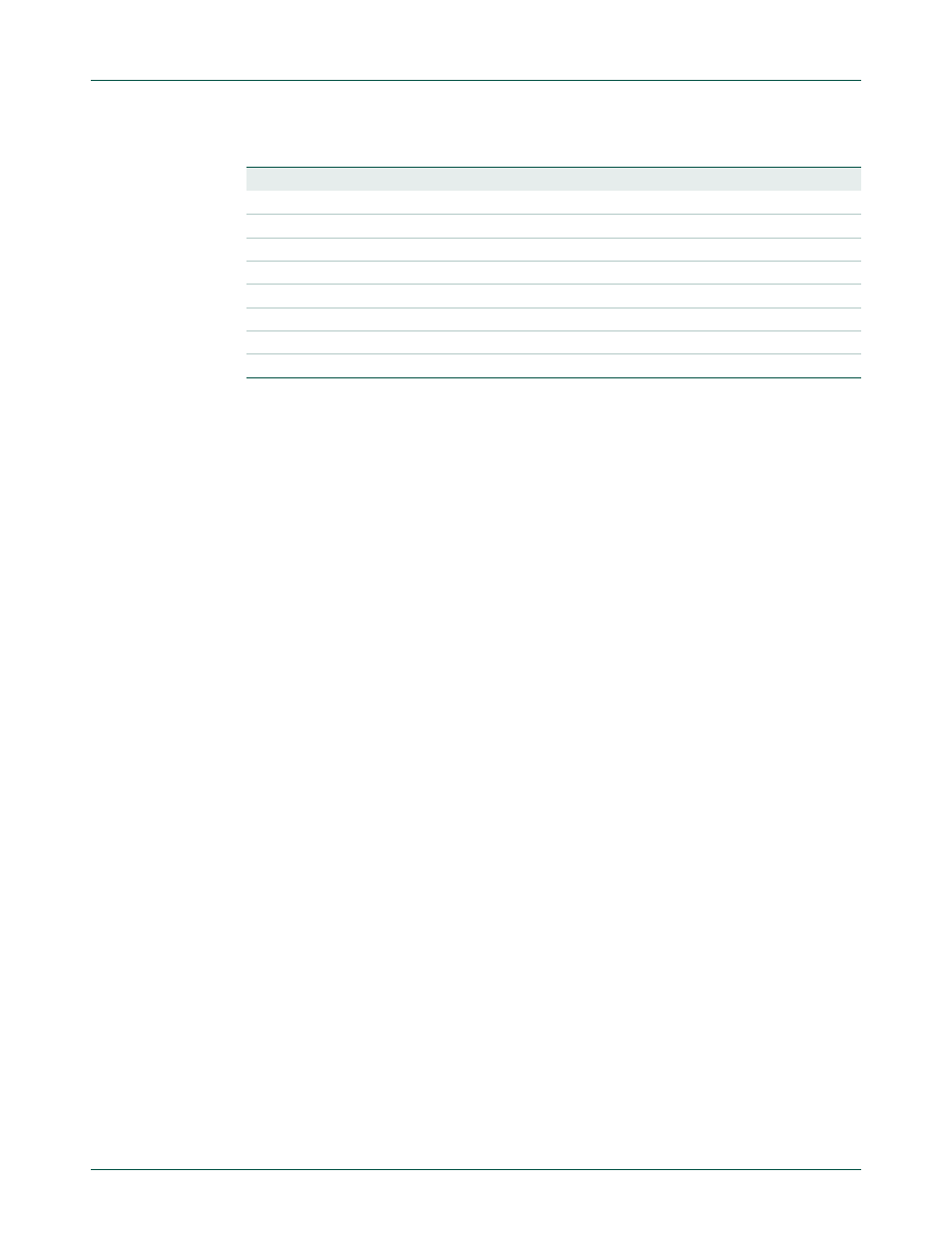

Table 578. Alarm registers

Name

Size

Description

Access

Address

ALSEC

6

Alarm value for Seconds

R/W

0xE002 4060

ALMIN

6

Alarm value for Minutes

R/W

0xE002 4064

ALHOUR

5

Alarm value for Hours

R/W

0xE002 4068

ALDOM

5

Alarm value for Day of Month

R/W

0xE002 406C

ALDOW

3

Alarm value for Day of Week

R/W

0xE002 4070

ALDOY

9

Alarm value for Day of Year

R/W

0xE002 4074

ALMON

4

Alarm value for Months

R/W

0xE002 4078

ALYEAR

12

Alarm value for Years

R/W

0xE002 407C