2 reset, Table 3–27, Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 31

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

31 of 792

NXP Semiconductors

UM10237

Chapter 3: LPC24XX System control

3.2 Reset

Reset has four sources on the LPC2400: the RESET pin, the Watchdog Reset, Power On

Reset (POR) and the Brown Out Detection circuit (BOD). The RESET pin is a Schmitt

trigger input pin. Assertion of chip Reset by any source, once the operating voltage attains

a usable level, starts the Wakeup Timer (see description in

this chapter), causing reset to remain asserted until the external Reset is de-asserted, the

oscillator is running, a fixed number of clocks have passed, and the flash controller has

completed its initialization. The reset logic is shown in

.

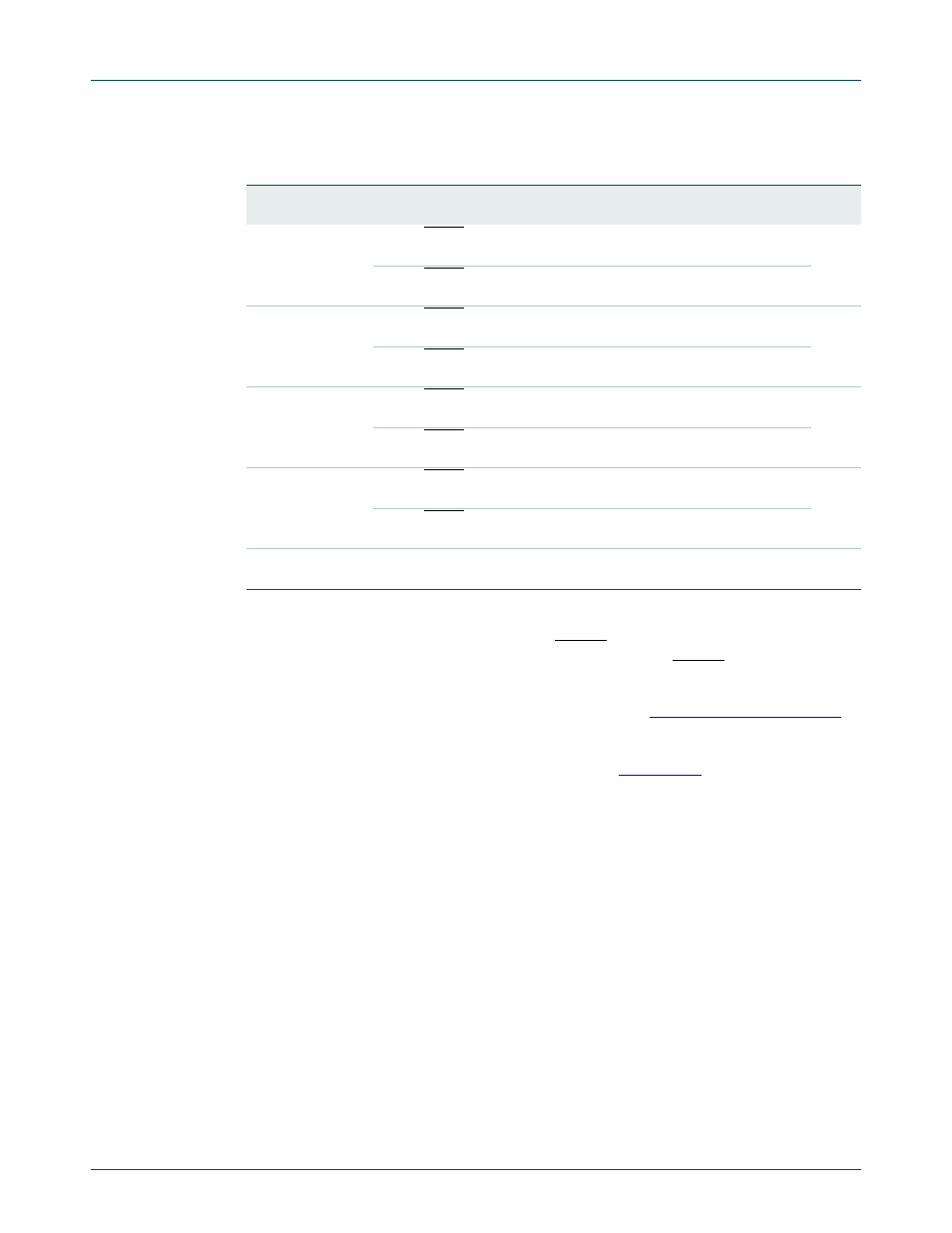

Table 27.

External Interrupt Polarity register (EXTPOLAR - address 0xE01F C14C) bit

description

Bit Symbol

Value Description

Reset

value

0

EXTPOLAR0 0

EINT0 is low-active or falling-edge sensitive (depending on

EXTMODE0).

0

1

EINT0 is high-active or rising-edge sensitive (depending on

EXTMODE0).

1

EXTPOLAR1 0

EINT1 is low-active or falling-edge sensitive (depending on

EXTMODE1).

0

1

EINT1 is high-active or rising-edge sensitive (depending on

EXTMODE1).

2

EXTPOLAR2 0

EINT2 is low-active or falling-edge sensitive (depending on

EXTMODE2).

0

1

EINT2 is high-active or rising-edge sensitive (depending on

EXTMODE2).

3

EXTPOLAR3 0

EINT3 is low-active or falling-edge sensitive (depending on

EXTMODE3).

0

1

EINT3 is high-active or rising-edge sensitive (depending on

EXTMODE3).

7:4 -

-

Reserved, user software should not write ones to reserved

bits. The value read from a reserved bit is not defined.

NA