Table 4–62, Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 64

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

64 of 792

NXP Semiconductors

UM10237

Chapter 4: LPC24XX Clocking and power control

processor up if it is asserted (eliminating the need to disable the interrupt if the wakeup

feature is not desirable in the application). Details of the wakeup operations are shown in

.

For an external interrupt pin to be a source that would wake up the microcontroller from

Power-down mode, it is also necessary to clear the corresponding interrupt flag (see

Section 3–3.1.2 “External Interrupt flag register (EXTINT - 0xE01F C140)”

).

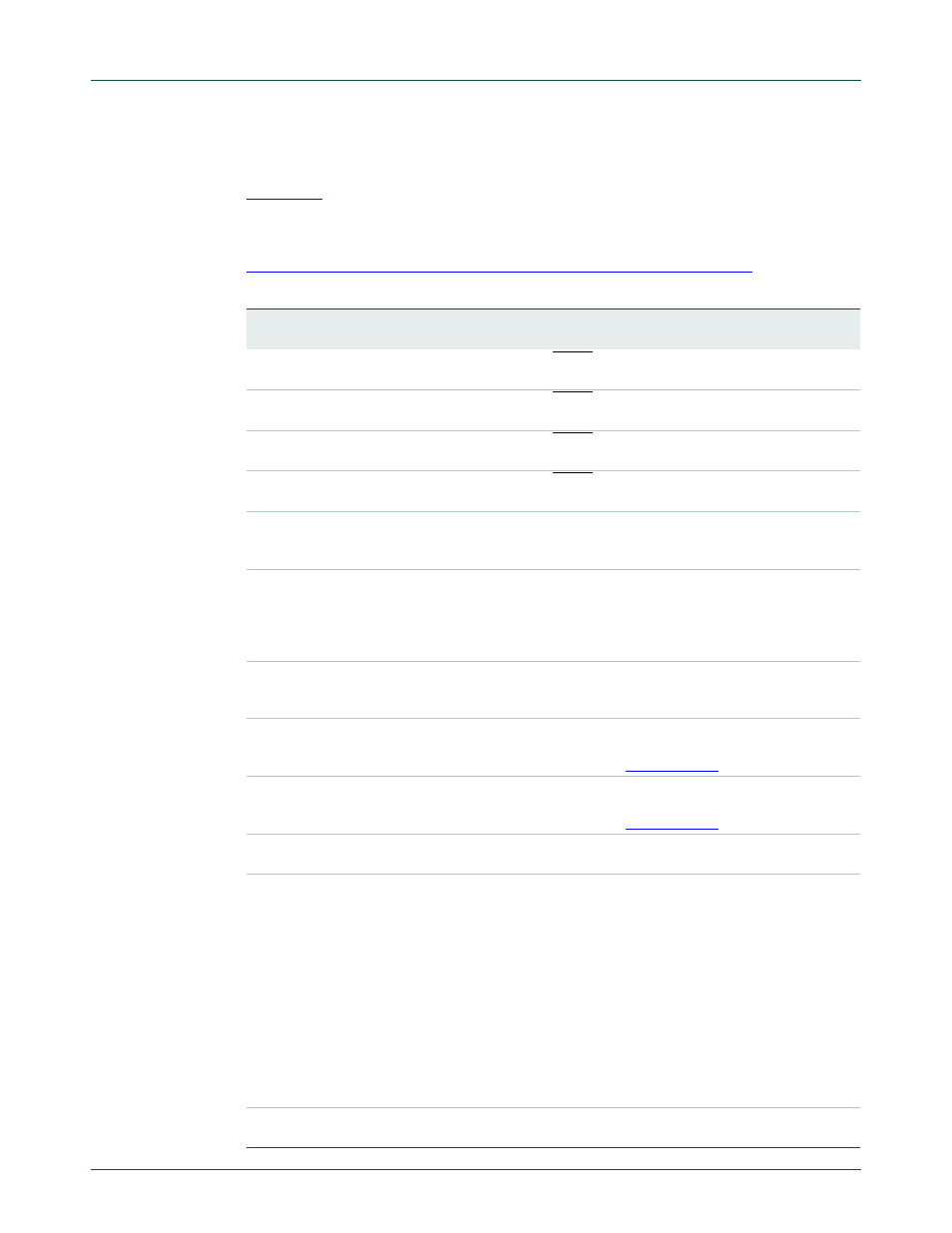

Table 62.

Interrupt Wakeup register (INTWAKE - address 0xE01F C144) bit description

Bit

Symbol

Description

Reset

value

0

EXTWAKE0

When one, assertion of EINT0 will wake up the processor from

Power-down mode.

0

1

EXTWAKE1

When one, assertion of EINT1 will wake up the processor from

Power-down mode.

0

2

EXTWAKE2

When one, assertion of EINT2 will wake up the processor from

Power-down mode.

0

3

EXTWAKE3

When one, assertion of EINT3 will wake up the processor from

Power-down mode.

0

4

ETHWAKE

When one, assertion of the Wake-up on LAN interrupt

(WakeupInt) of the Ethernet block will wake up the processor

from Power-down mode.

0

5

USBWAKE

When one, activity on the USB bus will wake up the processor

from Power-down mode. Any change of state on the USB data

pins will cause a wakeup when this bit is set. For details on the

relationship of USB to Power-down Mode and wakeup, see the

relevant USB chapter(s).

0

6

CANWAKE

When one, activity of the CAN bus will wake up the processor

from Power-down mode. Any change of state on the CAN

receive pins will cause a wakeup when this bit is set.

0

7

GPIO0WAKE

When one, specified activity on GPIO pins on port 0 enabled for

wakeup will wake up the processor from Power-down mode.

For configuring the port 0 pins, see

.

0

8

GPIO2WAKE

When one, specified activity on GPIO pins on port 2 enabled for

wakeup will wake up the processor from Power-down mode.

For configuring the port 2 pins, see

.

0

13:9

-

Reserved, user software should not write ones to reserved bits.

The value read from a reserved bit is not defined.

NA

14

BODWAKE

When one, Brown-Out Detect interrupt will wake up the

processor from Power-down mode.

Note: since there is a delay before execution begins, there is

no guarantee that execution will resume before V

DD(3V3)

has

fallen below the lower BOD threshold, which prevents

execution. If execution does resume, there is no guarantee of

how long the processor will continue execution before the lower

BOD threshold terminates execution. These issues depend on

the slope of the decline of V

DD(DCDC)(3V3)

. High decoupling

capacitance (between V

DD(DCDC)(3V3)

and ground) in the vicinity

of the LPC2400 will improve the likelihood that software will be

able to do what needs to be done when power is in the process

of being lost.

0

15

RTCWAKE

When one, assertion of an RTC interrupt will wake up the

processor from Power-down mode.

0