Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 106

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

106 of 792

NXP Semiconductors

UM10237

Chapter 6: LPC24XX Memory Accelerator Module (MAM)

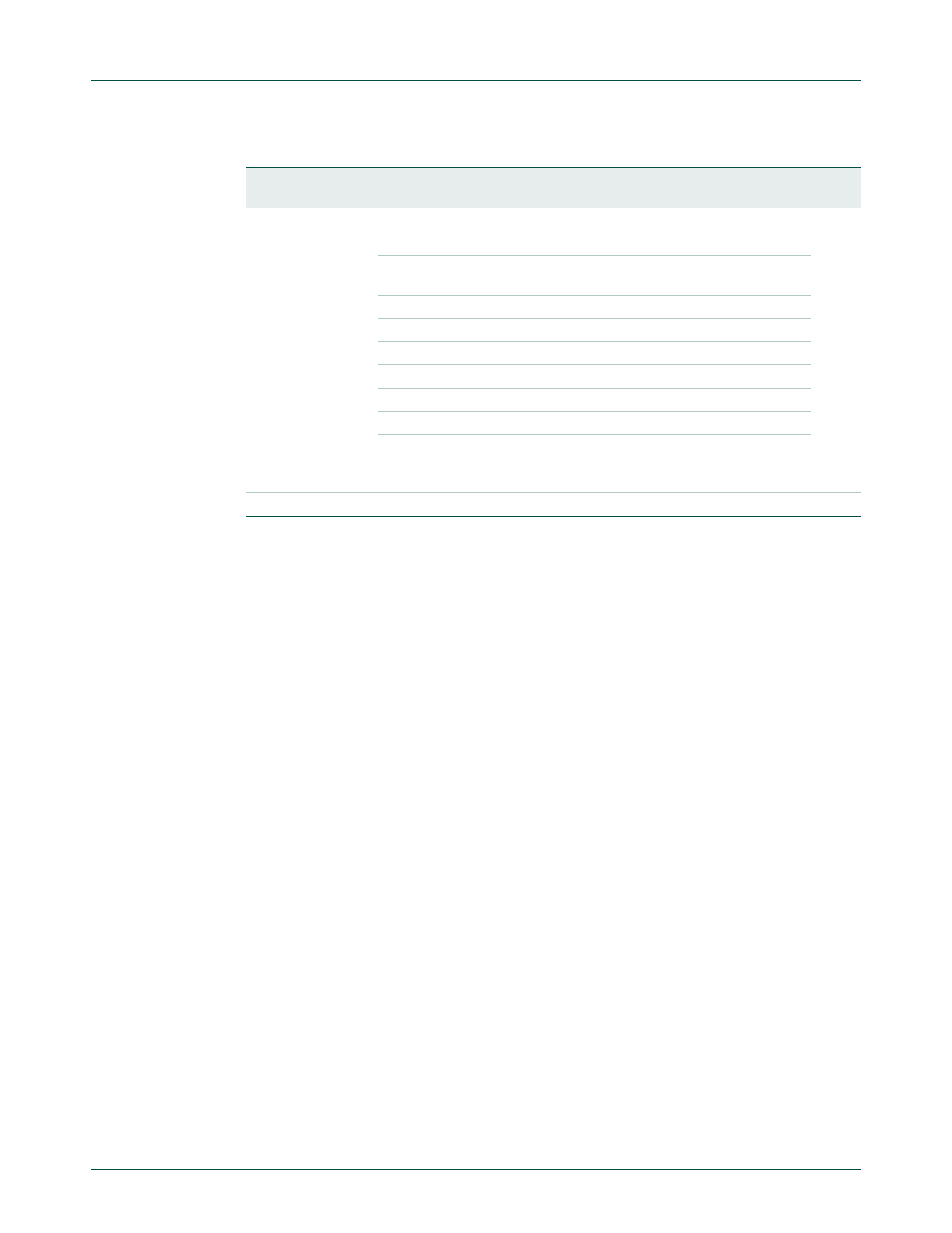

Table 100. MAM Timing register (MAMTIM - address 0xE01F C004) bit description

Bit

Symbol

Value Description

Reset

value

2:0

MAM_fetch_

cycle_timing

These bits set the duration of MAM fetch operations.

07

000

0 - Reserved

001

1 - MAM fetch cycles are 1 processor clock (CCLK) in

duration

010

2 - MAM fetch cycles are 2 CCLKs in duration

011

3 - MAM fetch cycles are 3 CCLKs in duration

100

4 - MAM fetch cycles are 4 CCLKs in duration

101

5 - MAM fetch cycles are 5 CCLKs in duration

110

6 - MAM fetch cycles are 6 CCLKs in duration

111

7 - MAM fetch cycles are 7 CCLKs in duration

Warning: These bits set the duration of MAM Flash fetch operations

as listed here. Improper setting of this value may result in incorrect

operation of the device.

7:3

-

-

Unused, always 0

0