Lpc2478 block diagram, Section 1–13, Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 15: Chapter 1: lpc24xx introductory information

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

15 of 792

NXP Semiconductors

UM10237

Chapter 1: LPC24XX Introductory information

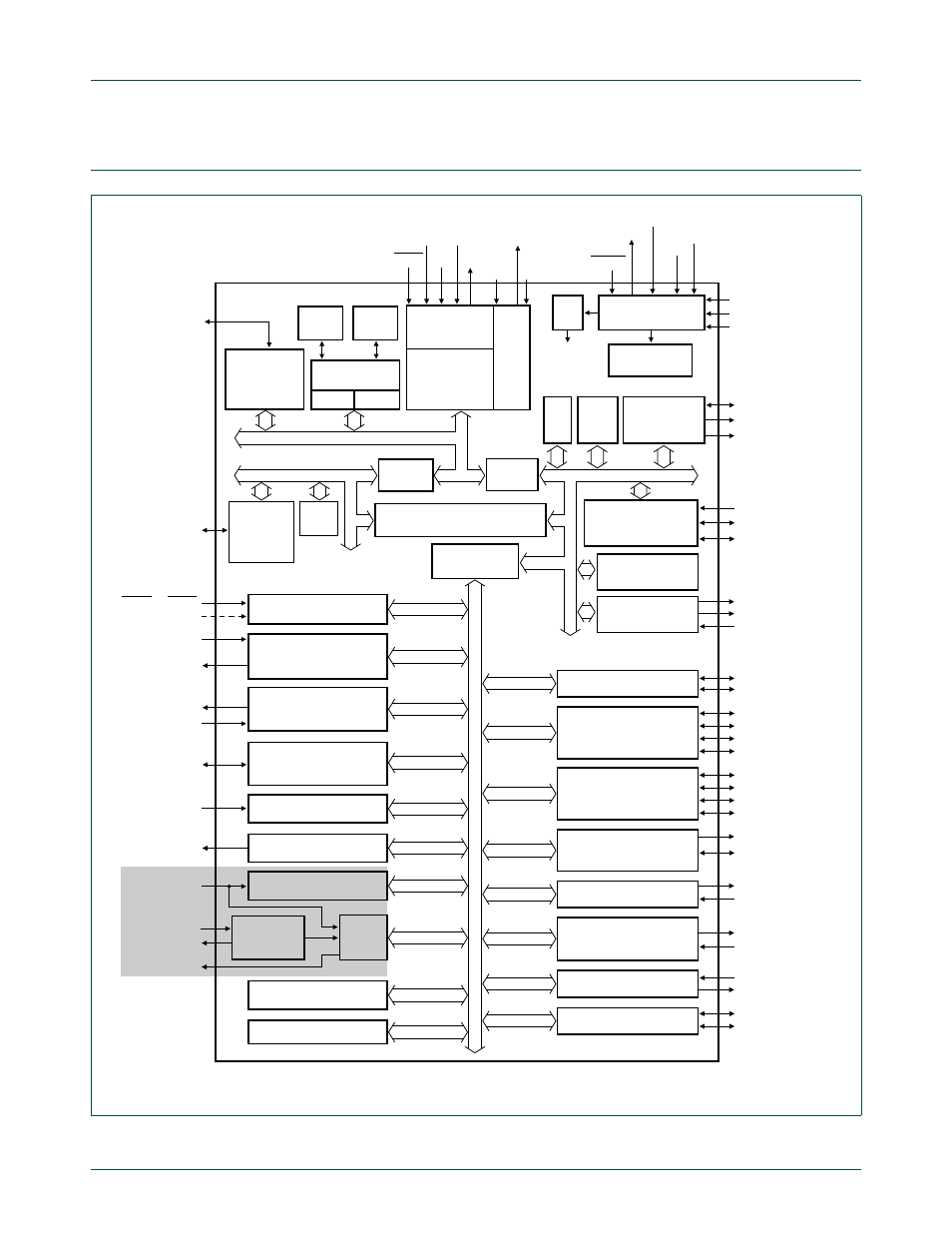

13. LPC2478 block diagram

Fig 5.

LPC2478 block diagram

power domain 2

LPC2478

A[23:0]

D[31:0]

EXTERNAL

MEMORY

CONTROLLER

ALARM

002aac805

PWM0, PWM1

ARM7TDMI-S

PLL

EINT3 to EINT0

FLASH

P3, P4

P0, P1, P2,

LEGACY GPI/O

64 PINS TOTAL

P0, P1

SCK0, SCK

3

× I2STX

3

× I2SRX

8

× LCD control

LCDVD[23:0]

LCDCLKIN

MOSI0, MOSI

SSEL0, SSEL

SCK1

MOSI1

MISO1

SSEL1

SCL0, SCL1, SCL2

8

× AD0

RTCX1

RTCX2

MCICLK, MCIPWR

RXD0, RXD2, RXD3

RD1, RD2

TD1, TD2

CAN1, CAN2

port1

XTAL1

TCK TDO

EXTIN0

XTAL2

RESET

TRST

TDI

TMS

HIGH-SPEED

GPI/O

160 PINS

TOTAL

port2

64 kB

SRAM

512 kB

FLASH

INTERNAL

CONTROLLERS

TEST/DEBUG

INTERFACE

EMULA

TION

TRA

CE MODULE

trace signals

AHB

BRIDGE

AHB

BRIDGE

ETHERNET

MAC WITH

DMA

16 kB

SRAM

MASTER

PORT

AHB TO

AHB BRIDGE

SLAVE

PORT

system

clock

SYSTEM

FUNCTIONS

INTERNAL RC

OSCILLATOR

V

DDA

V

DD(3V3)

V

DD(DCDC)(3V3)

VREF

V

SSA

, V

SSIO,

V

SSCORE

VIC

16 kB

SRAM

USB DEVICE/

HOST/OTG WITH

4 kB RAM AND DMA

GP DMA

CONTROLLER

LCD INTERFACE

WITH DMA

I

2

S INTERFACE

SSP0/SPI INTERFACE

MISO0, MISO

SSP1 INTERFACE

SD/MMC CARD

INTERFACE

MCICMD,

MCIDAT[3:0]

TXD0, TXD2, TXD3

UART0, UART2, UART3

UART1

TXD1, DTR1, RTS1

RXD1, DSR1, CTS1,

DCD1, RI1

I

2

C0, I

2

C1, I

2

C2

SDA0, SDA1, SDA2

EXTERNAL INTERRUPTS

CAPTURE/COMPARE

TIMER0/TIMER1/

TIMER2/TIMER3

A/D CONVERTER

D/A CONVERTER

2 kB BATTERY RAM

RTC

OSCILLATOR

REAL-

TIME

CLOCK

WATCHDOG TIMER

SYSTEM CONTROL

2

× CAP0/CAP1/

CAP2/CAP3

4

× MAT2/MAT3,

2

× MAT0,

3

× MAT1

6

× PWM0/PWM1

1

× PCAP0,

2

× PCAP1

AOUT

VBAT

AHB TO

APB BRIDGE

SRAM

MII/RMII

V

BUS

DBGEN

P0, P2

AHB2

AHB1

control lines