Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 208

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

208 of 792

NXP Semiconductors

UM10237

Chapter 10: LPC24XX General Purpose Input/Output (GPIO)

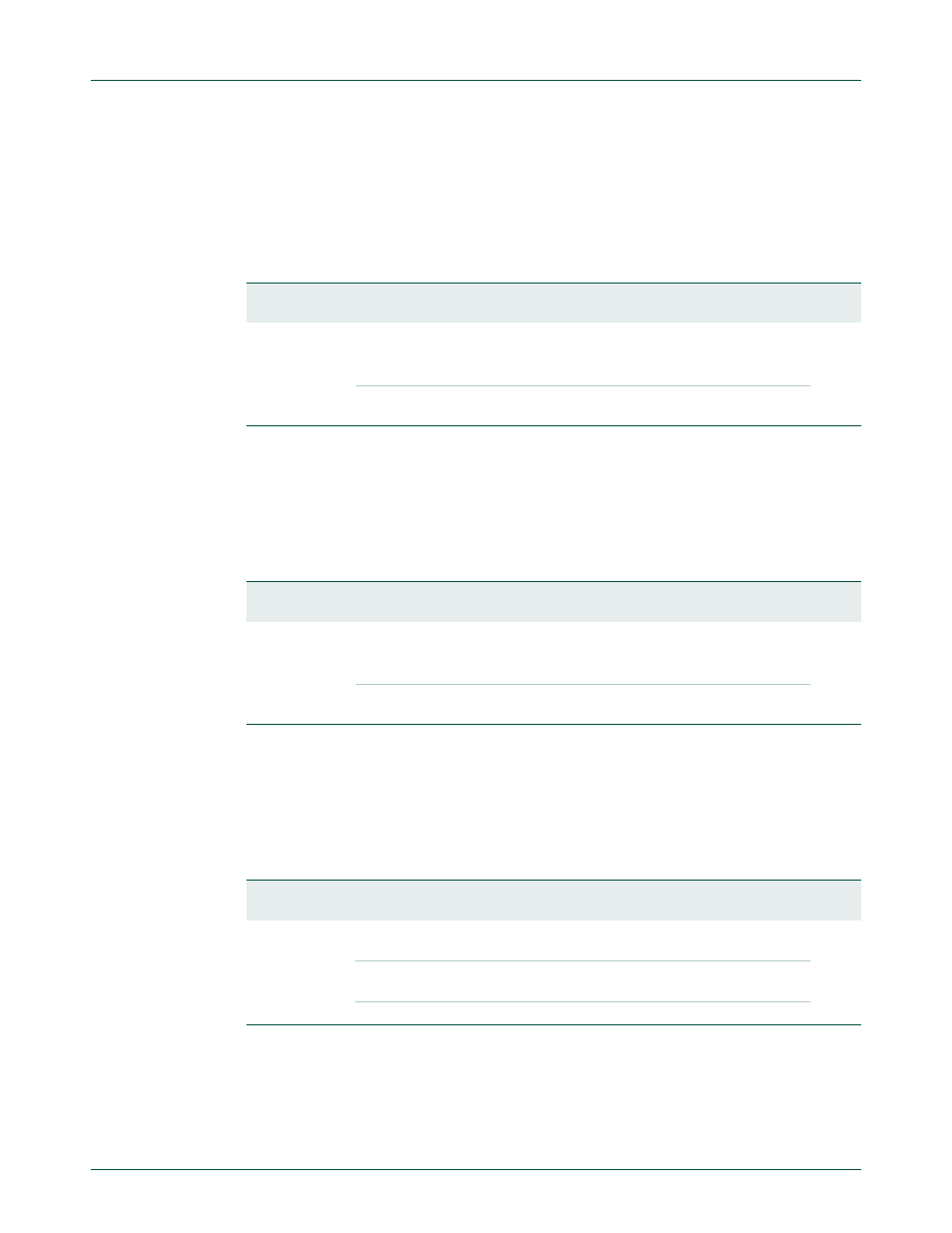

6.6.4 GPIO Interrupt Status for Rising edge register (IO0IntStatR - 0xE002 8084

and IO2IntStatR - 0xE002 80A4)

Each bit in these read-only registers indicates the rising edge interrupt status for the

corresponding port.

6.6.5 GPIO Interrupt Status for Falling edge register (IO0IntStatF - 0xE002 8088

and IO2IntStatF - 0xE002 80A8)

Each bit in these read-only registers indicates the rising edge interrupt status for the

corresponding port.

6.6.6 GPIO Interrupt Clear register (IO0IntClr - 0xE002 808C and IO2IntClr -

0xE002 80AC)

Writing a 1 into each bit in these write-only registers clears any interrupts for the

corresponding GPIO port pin.

Table 178. GPIO Status for Rising edge register (IO0IntStatR - address 0xE002 8084 and

IO2IntStatR - address 0xE002 80A4) bit description

Bit

Symbol

Value Description

Reset

value

31:0

P0xREI

and

P2xREI

0

Rising Edge Interrupt status. Bit 0 in IOxIntStatR corresponds to

pin Px.0, bit 31 in IOxIntStatR corresponds to pin Px.31.

Rising edge has not been detected on the corresponding pin.

0

1

An interrupt is generated due to a rising edge on the

corresponding pin.

Table 179. GPIO Status for Falling edge register (IO0IntStatF - address 0xE002 8088 and

IO2IntStatF - address 0xE002 80A8) bit description

Bit

Symbol

Value Description

Reset

value

31:0

P0xFEI

and

P2xFEI

0

Falling Edge Interrupt status. Bit 0 in IOxIntStatF corresponds to

pin Px.0, bit 31 in IOxIntStatF corresponds to pin Px.31.

Falling edge has not been detected on the corresponding pin.

0

1

An interrupt is generated due to a falling edge on the

corresponding pin.

Table 180. GPIO Status for Falling edge register (IO0IntClr - address 0xE002 808C and

IO2IntClr - address 0xE002 80AC) bit description

Bit

Symbol

Value Description

Reset

value

31:0

P0xCI

and

P2xCI

Clear GPIO port Interrupt. Bit 0 in IOxIntClr corresponds to pin

Px.0, bit 31 in IOxIntClr corresponds to pin Px.31.

0

0

Corresponding bit in IOxIntStatR and/or IOxIntStatF is

unchanged.

1

Corresponding bit in IOxIntStatR and IOxStatF is cleared to 0.