Table 25–560, Table 25–561, Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 641

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

641 of 792

NXP Semiconductors

UM10237

Chapter 25: LPC24XX Pulse Width Modulator PWM0/PWM1

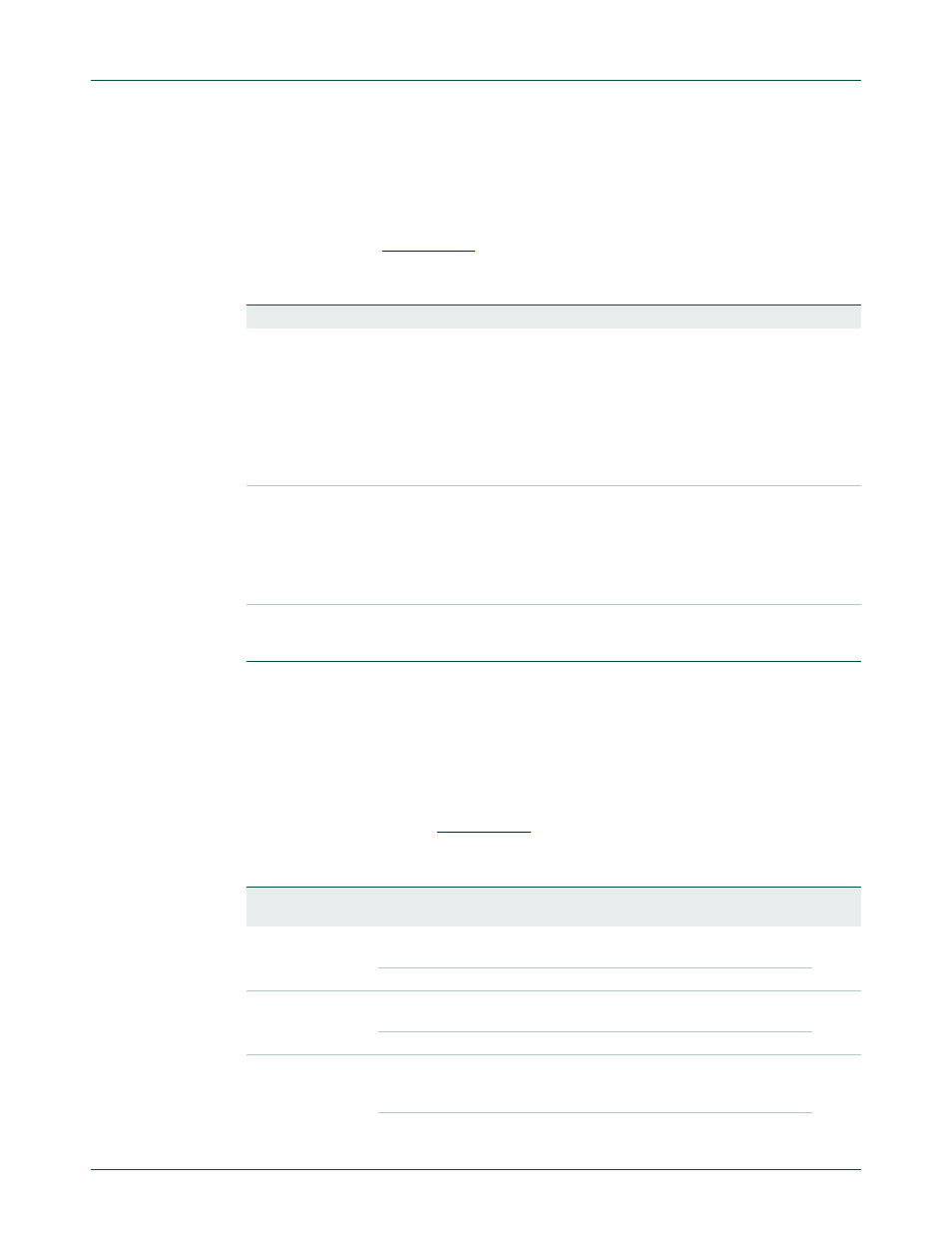

6.3 PWM Count Control Register (PWM0CTCR - 0xE001 4070 and

PWM1CTCR 0xE001 8070)

The Count Control Register (CTCR) is used to select between Timer and Counter mode,

and in Counter mode to select the pin and edge(s) for counting. The function of each of

the bits is shown in

.

[1]

PCAP input signal frequency must not exceed PCLK/4. When the PWM clock is supplied via the PCAP pin,

at no time high(low) level of the signal on this pin can last less than 1/(2

×

PCLK).

6.4 PWM Match Control Register (PWM0MCR - 0xE001 4014 and

PWM1MCR 0xE001 8014)

The PWM Match Control registers are used to control what operations are performed

when one of the PWM Match registers matches the PWM Timer Counter. The function of

each of the bits is shown in

Table 560: PWM Count control Register (PWM0TCR - address 0xE001 4004 and PWM1CTCR

address 0xE001 8004) bit description

Bit

Symbol

Description

Reset Value

1:0

Counter/

Timer Mode

00: Timer Mode: the TC is incremented when the

Prescale Counter matches the Prescale register.

01: Counter Mode: the TC is incremented on rising

edges of the PCAP input selected by bits 3:2.

10: Counter Mode: the TC is incremented on falling

edges of the PCAP input selected by bits 3:2.

11: Counter Mode: the TC is incremented on both edges

of the PCAP input selected by bits 3:2.

00

3:2

Count Input

Select

When bits 1:0 are not 00, these bits select which PCAP

pin carries the signal used to increment the TC.

For PWM0: 00 = PCAP0.0 (Other combinations are

reserved)

For PWM1: 00 = PCAP1.0, 01 = PCAP1.1(Other

combinations are reserved)

00

7:4

-

Reserved, user software should not write ones to

reserved bits. The value read from a reserved bit is not

defined.

NA

Table 561: Match Control Register (PWM0MCR - address 0xE000 4014 and PWM1MCR -

address 0xE000 8014) bit description

Bit

Symbol

Value Description

Reset

Value

0

PWMMR0I

1

Interrupt on PWMMR0: an interrupt is generated when

PWMMR0 matches the value in the PWMTC.

0

0

This interrupt is disabled.

1

PWMMR0R 1

Reset on PWMMR0: the PWMTC will be reset if PWMMR0

matches it.

0

0

This feature is disabled.

2

PWMMR0S 1

Stop on PWMMR0: the PWMTC and PWMPC will be stopped

and PWMTCR bt 0 will be set to 0 if PWMMR0 matches the

PWMTC.

0

0

This feature is disabled