1 prepare sector(s) for write operation, Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 692

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

692 of 792

NXP Semiconductors

UM10237

Chapter 30: LPC24XX Flash memory programming firmware

As per the ARM specification (The ARM Thumb Procedure Call Standard SWS ESPC

0002 A-05) up to 4 parameters can be passed in the r0, r1, r2 and r3 registers

respectively. Additional parameters are passed on the stack. Up to 4 parameters can be

returned in the r0, r1, r2 and r3 registers respectively. Additional parameters are returned

indirectly via memory. Some of the IAP calls require more than 4 parameters. If the ARM

suggested scheme is used for the parameter passing/returning then it might create

problems due to difference in the C compiler implementation from different vendors. The

suggested parameter passing scheme reduces such risk.

The Flash memory is not accessible during a write or erase operation. IAP commands,

which results in a Flash write/erase operation, use 32 bytes of space in the top portion of

the on-chip RAM for execution. The user program should not be use this space if IAP

Flash programming is permitted in the application.

10.1 Prepare sector(s) for write operation

This command makes Flash write/erase operation a two step process.

Table 620. IAP Command Summary

IAP Command

Command Code

Described in

Prepare sector(s) for write operation

50

10

Copy RAM to Flash

51

10

Erase sector(s)

52

10

Blank check sector(s)

53

10

Read Part ID

54

10

Read Boot code version

55

10

Compare

56

10

Reinvoke ISP

57

10

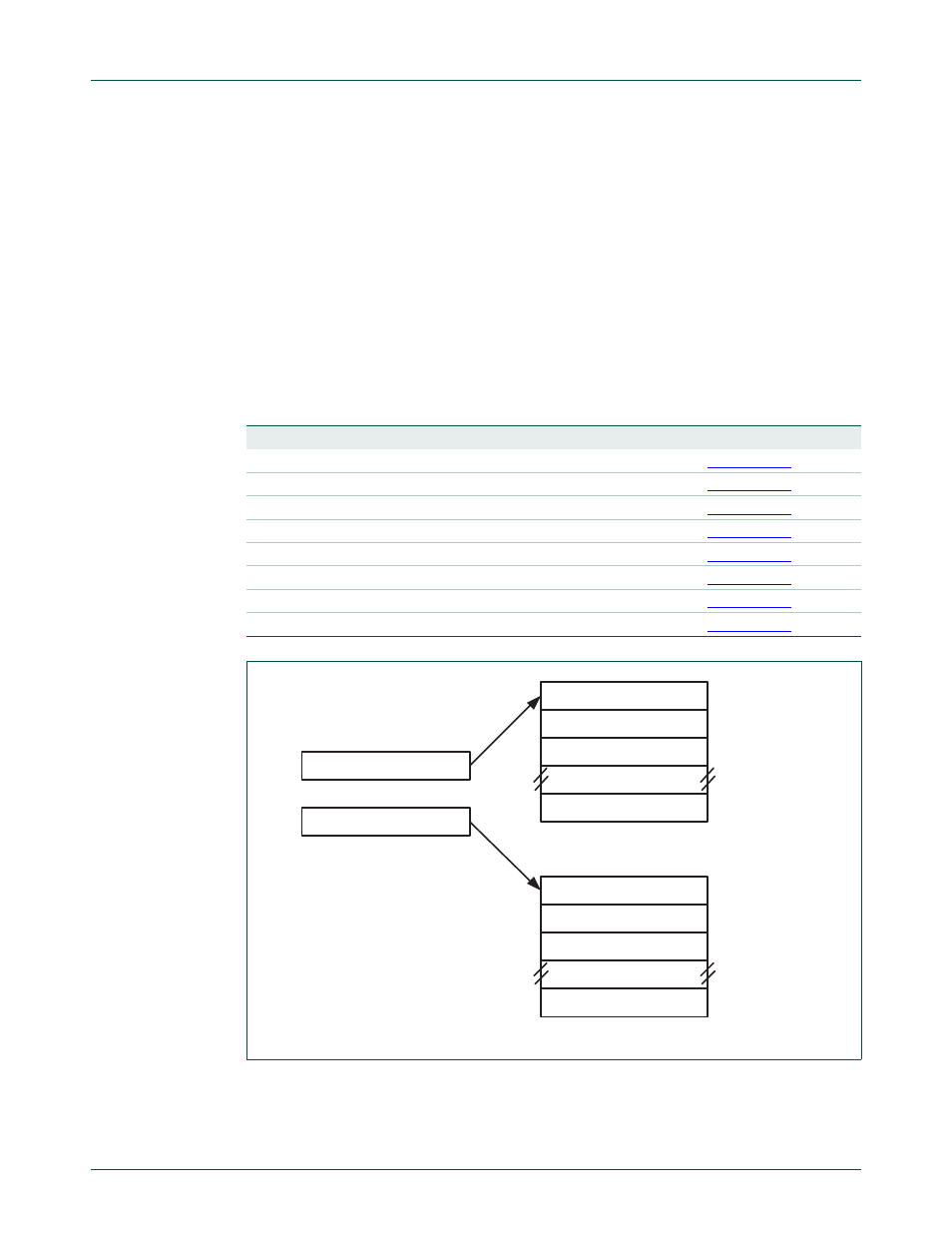

Fig 140. IAP parameter passing

COMMAND CODE

PARAMETER 1

PARAMETER 2

PARAMETER n

STATUS CODE

RESULT 1

RESULT 2

RESULT n

command

parameter table

command

result table

ARM REGISTER r0

ARM REGISTER r1