Global acceptance filter, Acceptance filter modes, 1 acceptance filter off mode – NXP Semiconductors LPC24XX UM10237 User Manual

Page 497: Nxp semiconductors

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

497 of 792

NXP Semiconductors

UM10237

Chapter 18: LPC24XX CAN controllers CAN1/2

11. Global acceptance filter

This block provides lookup for received Identifiers (called Acceptance Filtering in CAN

terminology) for all the CAN Controllers. It includes a 512

× 32 (2 kB) RAM in which

software maintains one to five tables of Identifiers. This RAM can contain up to 1024

Standard Identifiers or 512 Extended Identifiers, or a mixture of both types.

12. Acceptance filter modes

The Acceptance Filter can be put into different modes by setting the according AccOff,

AccBP, and eFCAN bits in the Acceptance Filter Mode Register (

“Acceptance Filter Mode Register (AFMR - 0xE003 C000)”

). During each mode the

access to the Configuration Register and the ID Look-up table is handled differently.

[1]

The whole ID Look-up Table RAM is only word accessible.

[2]

During the Operating Mode of the Acceptance Filter the Look-up Table can be accessed only to disable or

enable Messages.

A write access to all section configuration registers is only possible during the Acceptance

Filter Off and Bypass Mode. Read access is allowed in all Acceptance Filter Modes.

12.1 Acceptance filter Off mode

The Acceptance Filter Off Mode is typically used during initialization. During this mode an

unconditional access to all registers and to the Look-up Table RAM is possible. With the

Acceptance Filter Off Mode, CAN messages are not accepted and therefore not stored in

the Receive Buffers of active CAN Controllers.

8

BS1

When 1, the CAN controller is currently not involved/prohibited from bus

activity (same as BS in CAN1GSR).

0

9

BS2

When 1, the CAN controller is currently not involved/prohibited from bus

activity (same as BS in CAN1GSR).

0

31:10 -

Reserved, user software should not write ones to reserved bits. The

value read from a reserved bit is not defined.

NA

Table 440. Central Miscellaneous Status Register (CANMSR - address 0xE004 0008) bit

description

Bit

Symbol Description

Reset

Value

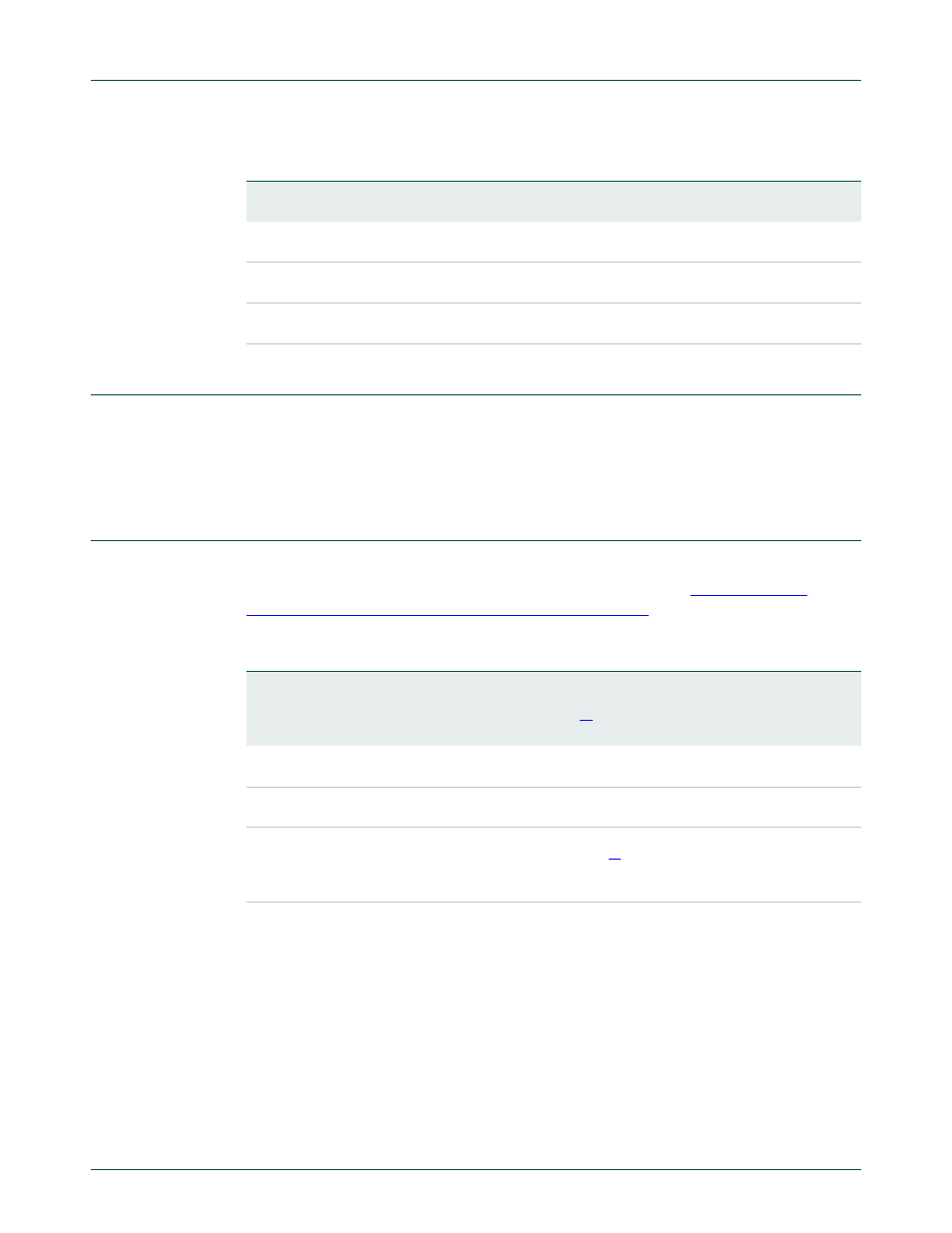

Table 441. Acceptance filter modes and access control

Acceptance

filter mode

Bit

AccOff

Bit

AccBP

Acceptance

filter state

ID Look-up

table

RAM

Acceptanc

e filter

config.

registers

CAN controller

message receive

interrupt

Off Mode

1

0

reset &

halted

r/w access

from CPU

r/w access

from CPU

no messages

accepted

Bypass

Mode

X

1

reset &

halted

r/w access

from CPU

r/w access

from CPU

all messages

accepted

Operating

Mode and

FullCAN

Mode

0

0

running

read only

from CPU

access from

Acceptance

filter only

hardware

acceptance filtering