Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 407

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

407 of 792

NXP Semiconductors

UM10237

Chapter 15: LPC24XX USB OTG controller

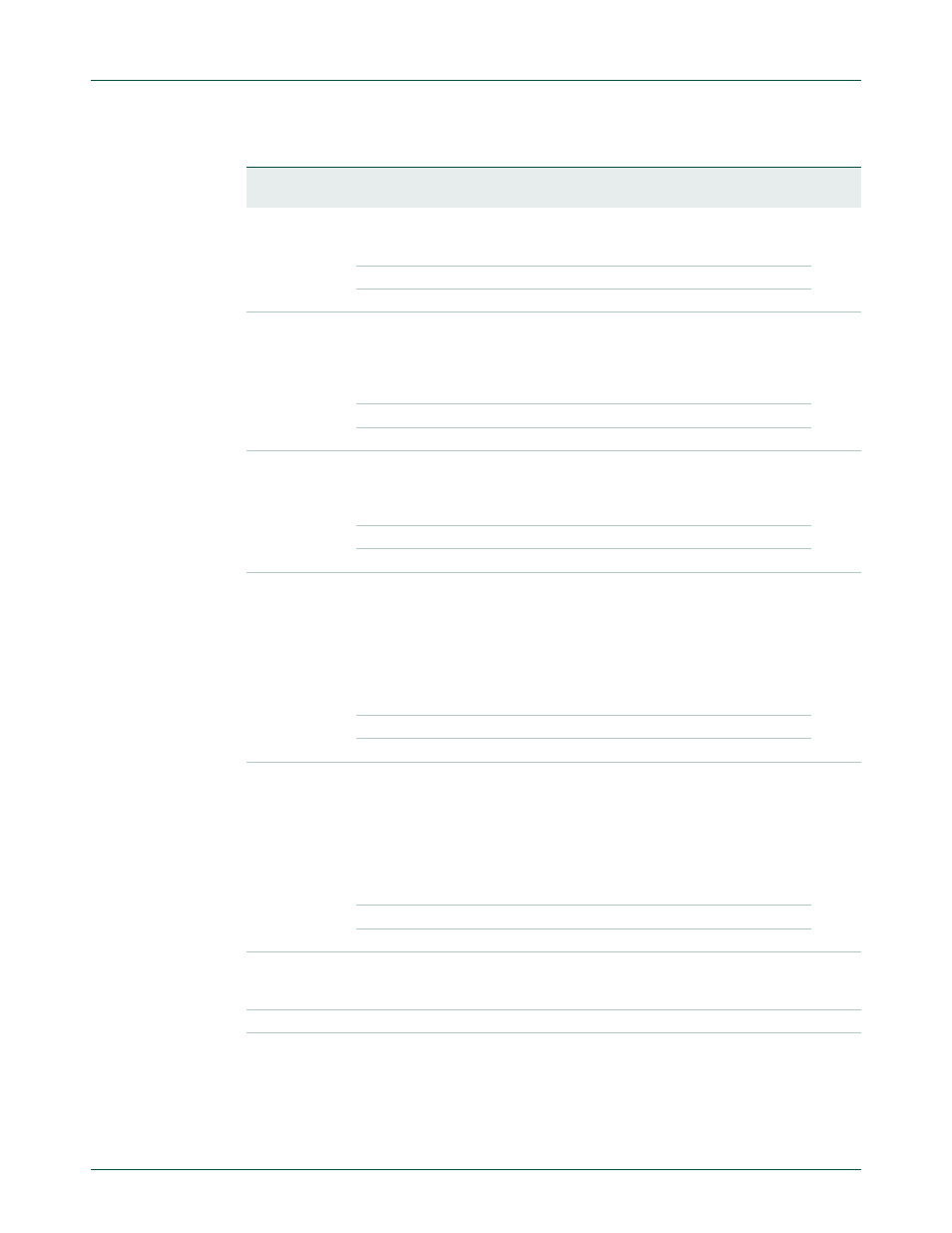

Table 372. I2C status register (I2C_STS - address 0xFFE0 C304) bit description

Bit

Symbol Value Description

Reset

Value

0

TDI

Transaction Done Interrupt. This flag is set if a transaction

completes successfully. It is cleared by writing a one to bit 0 of

the status register. It is unaffected by slave transactions.

0

0

Transaction has not completed.

1

Transaction completed.

1

AFI

Arbitration Failure Interrupt. When transmitting, if the SDA is low

when SDAOUT is high, then this I

2

C has lost the arbitration to

another device on the bus. The Arbitration Failure bit is set when

this happens. It is cleared by writing a one to bit 1 of the status

register.

0

0

No arbitration failure on last transmission.

1

Arbitration failure occurred on last transmission.

2

NAI

No Acknowledge Interrupt. After every byte of data is sent, the

transmitter expects an acknowledge from the receiver. This bit is

set if the acknowledge is not received. It is cleared when a byte

is written to the master TX FIFO.

0

0

Last transmission received an acknowledge.

1

Last transmission did not receive an acknowledge.

3

DRMI

Master Data Request Interrupt. Once a transmission is started,

the transmitter must have data to transmit as long as it isn’t

followed by a stop condition or it will hold SCL low until more

data is available. The Master Data Request bit is set when the

master transmitter is data-starved. If the master TX FIFO is

empty and the last byte did not have a STOP condition flag, then

SCL is held low until the CPU writes another byte to transmit.

This bit is cleared when a byte is written to the master TX FIFO.

0

0

Master transmitter does not need data.

1

Master transmitter needs data.

4

DRSI

Slave Data Request Interrupt. Once a transmission is started,

the transmitter must have data to transmit as long as it isn’t

followed by a STOP condition or it will hold SCL low until more

data is available. The Slave Data Request bit is set when the

slave transmitter is data-starved. If the slave TX FIFO is empty

and the last byte transmitted was acknowledged, then SCL is

held low until the CPU writes another byte to transmit. This bit is

cleared when a byte is written to the slave Tx FIFO.

0

0

Slave transmitter does not need data.

1

Slave transmitter needs data.

5

Active

Indicates whether the bus is busy. This bit is set when a START

condition has been seen. It is cleared when a STOP condition is

seen..

0

6

SCL

The current value of the SCL signal.

-

7

SDA

The current value of the SDA signal.

-