4 endpoint interrupt registers, Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 343

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

343 of 792

NXP Semiconductors

UM10237

Chapter 13: LPC24XX USB device controller

9.3.6 USB Device Interrupt Priority register (USBDevIntPri - 0xFFE0 C22C)

Writing one to a bit in this register causes the corresponding interrupt to be routed to the

USB_INT_REQ_HP interrupt line. Writing zero causes the interrupt to be routed to the

USB_INT_REQ_LP interrupt line. Either the EP_FAST or FRAME interrupt can be routed

to USB_INT_REQ_HP, but not both. If the software attempts to set both bits to one, no

interrupt will be routed to USB_INT_REQ_HP. USBDevIntPri is a write only register.

9.4 Endpoint interrupt registers

The registers in this group facilitate handling of endpoint interrupts. Endpoint interrupts are

used in Slave mode operation.

9.4.1 USB Endpoint Interrupt Status register (USBEpIntSt - 0xFFE0 C230)

Each physical non-isochronous endpoint is represented by a bit in this register to indicate

that it has generated an interrupt. All non-isochronous OUT endpoints generate an

interrupt when they receive a packet without an error. All non-isochronous IN endpoints

generate an interrupt when a packet is successfully transmitted, or when a NAK

handshake is sent on the bus and the interrupt on NAK feature is enabled (see

13–11.3 “Set Mode (Command: 0xF3, Data: write 1 byte)” on page 365

). A bit set to one in

this register causes either the EP_FAST or EP_SLOW bit of USBDevIntSt to be set

depending on the value of the coreesponding bit of USBEpDevIntPri. USBEpIntSt is a

read only register.

Note that for Isochronous endpoints, handling of packet data is done when the FRAME

interrupt occurs.

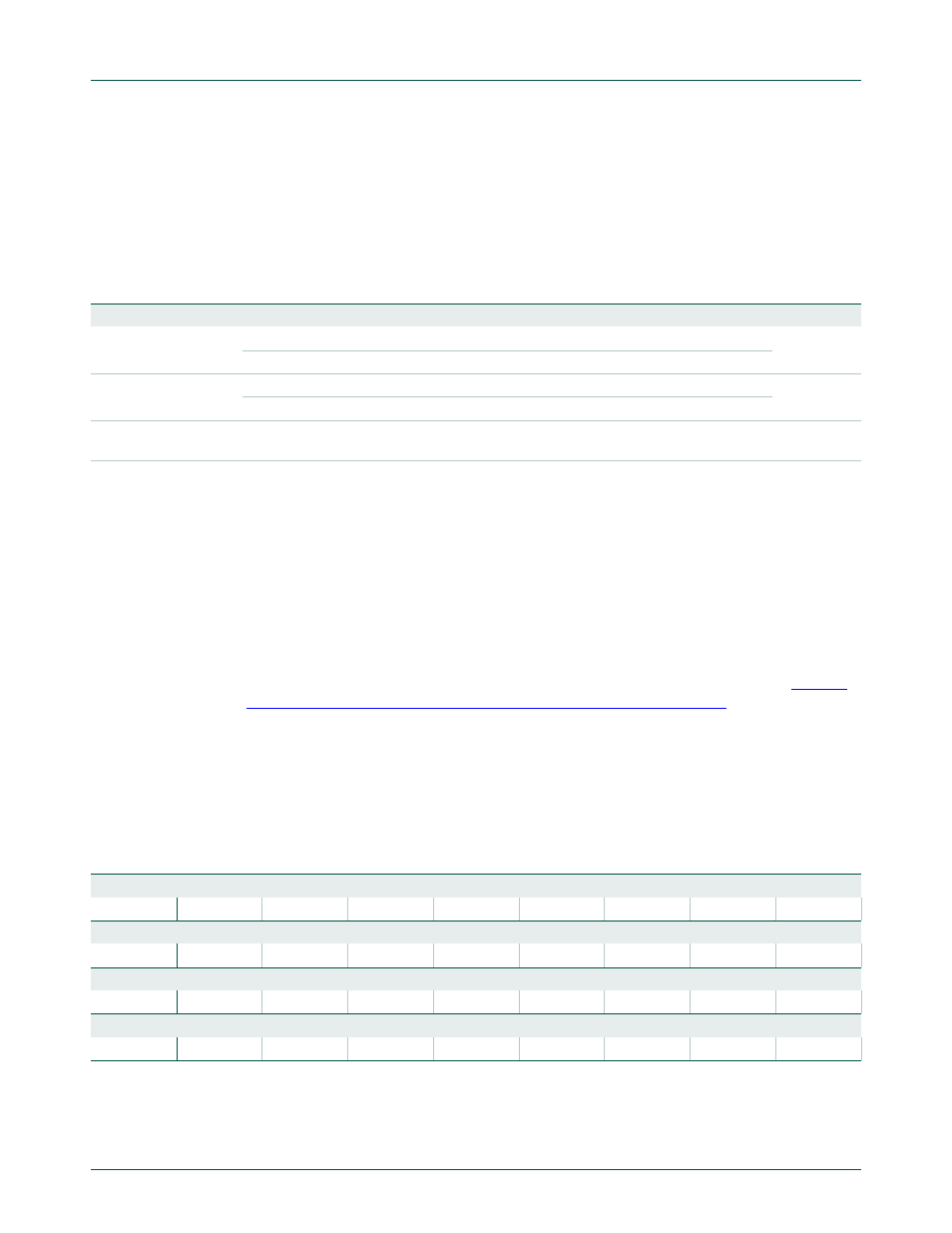

Table 306. USB Device Interrupt Priority register (USBDevIntPri - address 0xFFE0 C22C) bit description

Bit

Symbol

Value

Description

Reset value

0

FRAME

0

FRAME interrupt is routed to USB_INT_REQ_LP.

0

1

FRAME interrupt is routed to USB_INT_REQ_HP.

1

EP_FAST

0

EP_FAST interrupt is routed to USB_INT_REQ_LP.

0

1

EP_FAST interrupt is routed to USB_INT_REQ_HP.

7:2

-

-

Reserved, user software should not write ones to reserved bits. The value

read from a reserved bit is not defined.

NA

Table 307. USB Endpoint Interrupt Status register (USBEpIntSt - address 0xFFE0 C230) bit allocation

Reset value: 0x0000 0000

Bit

31

30

29

28

27

26

25

24

Symbol

EP15TX

EP15RX

EP14TX

EP14RX

EP13TX

EP13RX

EP12TX

EP12RX

Bit

23

22

21

20

19

18

17

16

Symbol

EP11TX

EP11RX

EP10TX

EP10RX

EP9TX

EP9RX

EP8TX

EP8RX

Bit

15

14

13

12

11

10

9

8

Symbol

EP7TX

EP7RX

EP6TX

EP6RX

EP5TX

EP5RX

EP4TX

EP4RX

Bit

7

6

5

4

3

2

1

0

Symbol

EP3TX

EP3RX

EP2TX

EP2RX

EP1TX

EP1RX

EP0TX

EP0RX