Section 18–8.1, Can2mod - 0xe004 8000), Mode – NXP Semiconductors LPC24XX UM10237 User Manual

Page 475: Nxp semiconductors

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

475 of 792

NXP Semiconductors

UM10237

Chapter 18: LPC24XX CAN controllers CAN1/2

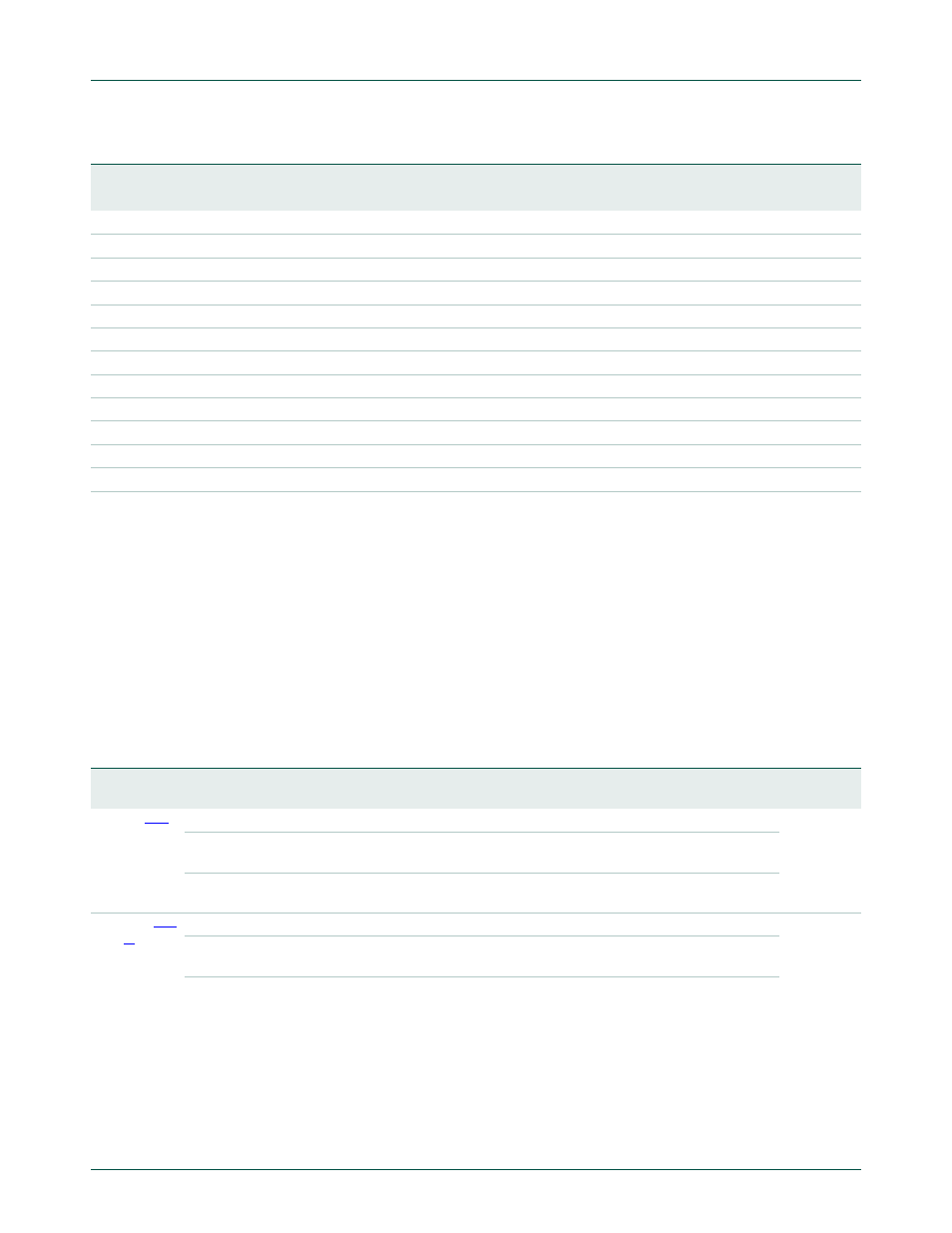

In the following register tables, the column “Reset Value” shows how a hardware reset

affects each bit or field, while the column “RM Set” indicates how each bit or field is

affected if software sets the RM bit, or RM is set because of a Bus-Off condition. Note that

while hardware reset sets RM, in this case the setting noted in the “Reset Value” column

prevails over that shown in the “RM Set” column, in the few bits where they differ. In both

columns, X indicates the bit or field is unchanged.

8.1

Mode

Register (CAN1MOD - 0xE004 4000, CAN2MOD - 0xE004 8000)

The contents of the Mode Register are used to change the behavior of the CAN

Controller. Bits may be set or reset by the CPU that uses the Mode Register as a

read/write memory. Reserved Bits are read as 0 and should be written as 0.

IER

Interrupt Enable

Interrupt Enable

Interrupt Enable

Interrupt Enable

BTR

Bus Timing

-

Bus Timing

Bus Timing

EWL

Error Warning Limit

-

Error Warning Limit

Error Warning Limit

SR

Status

-

Status

-

RFS

Rx Info and Index

-

Rx Info and Index

Rx Info and Index

RID

Rx Identifier

-

Rx Identifier

Rx Identifier

RDA

Rx Data

-

Rx Data

Rx Data

RDB

Rx Info and Index

-

Rx Info and Index

Rx Info and Index

TFI1

Tx Info1

Tx Info

Tx Info

Tx Info

TID1

Tx Identifier

Tx Identifier

Tx Identifier

Tx Identifier

TDA1

Tx Data

Tx Data

Tx Data

Tx Data

TDB1

Tx Data

Tx Data

Tx Data

Tx Data

Table 419. Access to CAN1 and CAN2 controller registers

Generic

Name

Operating Mode

Reset Mode

Read

Write

Read

Write

Table 420. Mode register (CAN1MOD - address 0xE004 4000, CAN2MOD - address 0xE004 8000) bit description

Bit Symbol

Value

Function

Reset

Value

RM

Set

0

RM

Reset Mode.

1

1

0(normal)

The CAN Controller is in the Operating Mode, and certain registers can not be

written.

1(reset)

CAN operation is disabled, writable registers can be written and the current

transmission/reception of a message is aborted.

1

LOM

Listen Only Mode.

0

x

0(normal)

The CAN controller acknowledges a successfully received message on the

CAN bus. The error counters are stopped at the current value.

1(listen only)

The controller gives no acknowledgment, even if a message is successfully

received. Messages cannot be sent, and the controller operates in “error

passive” mode. This mode is intended for software bit rate detection and “hot

plugging”.